IBM با تراشههای هوش مصنوعی، به یکهتازی انویدیا پایان میدهد

آیبیام یکی از پیشروان صنعت کامپیوتر کوانتومی محسوب میشود و اخیراً تحقیقاتی انجام داده که نشان از نوع تفکر این شرکت درمورد راهکارهای پردازش هوش مصنوعی دارد.

اگر چشمانداز IBM به سرانجام دلخواه این شرکت برسد، آیندهی هوش مصنوعی حول پردازنده گرافیکی متمرکز نخواهد شد و درعوض تراشههای آنالوگ با سیگنال مختلط، با بهبود بهرهوری انرژی و عملکرد رقابتی، روی کار خواهند آمد.

IBM با انتشار مقالهی تحقیقاتی در Nature Electronics اعلام کرد آیندهی استنباط هوش مصنوعی میتواند ازطریق تراشهای که حافظهی تغییر فاز(PCM) را با مدارهای دیجیتال ترکیب میکند، تأمین شود. طبق این مقاله، ضریب ماتریس-بردار(یکی از بارهای کاری اصلی برای استنتاج هوش مصنوعی) میتواند مستقیماً روی وزنهای ذخیرهشده در تراشه انجام شود.

کاهش توان مورد نیاز مدارهای منفعل و آنالوگ در سناریوی مدنظر IBM میتواند توان کلی موردنیاز برای انجام موفقیتآمیز محاسبات ماتریس را کاهش داده یا حداقل انرژی مازاد بخشهای آنالوگ پردازنده را بهطرف مدارهای دیجیتال دیگر هدایت کند.

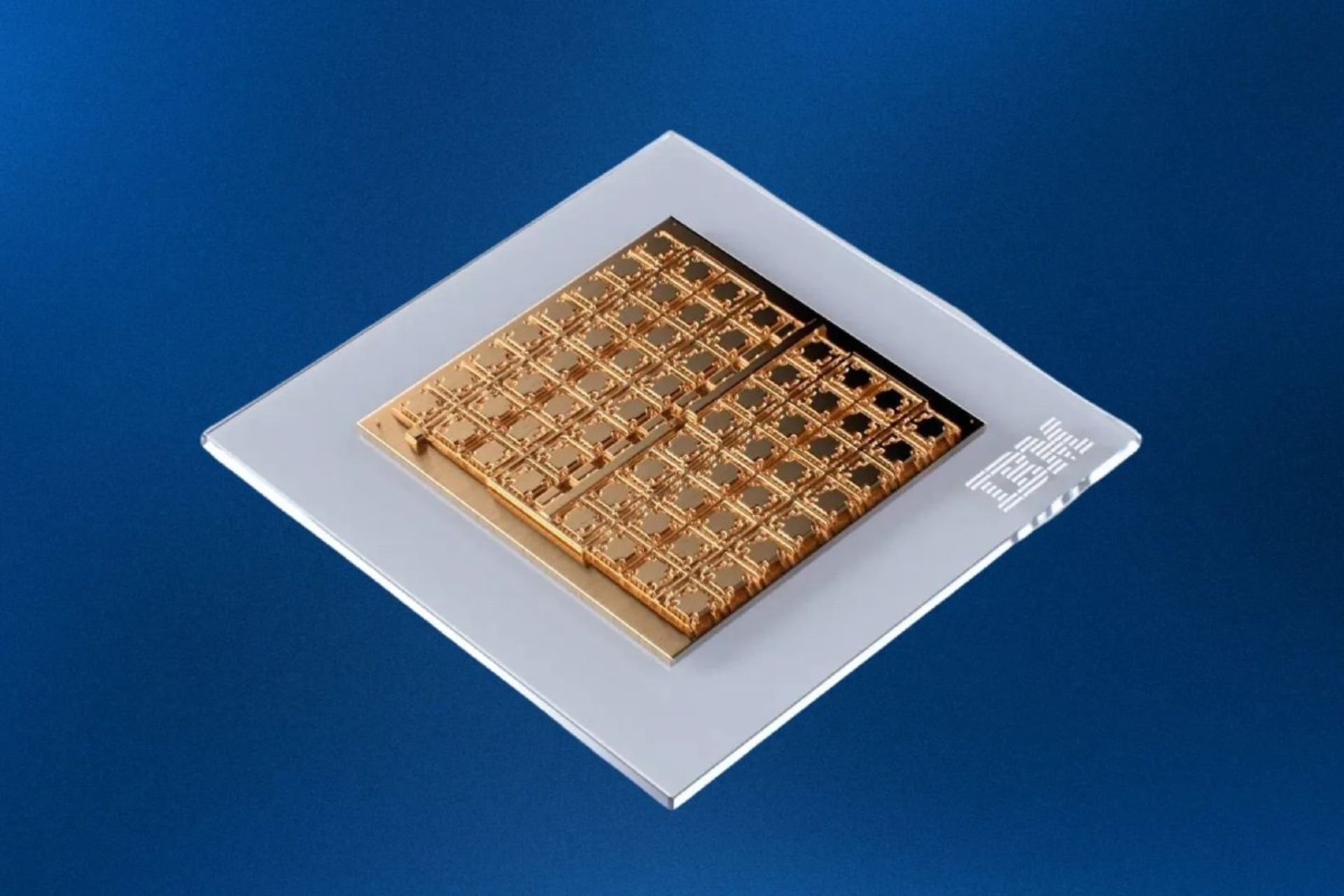

جدیدترین نسخهی تراشهی هیبریدی IBM که بهعنوان بخشی از پروژه هرمس این شرکت توسعه یافته، ۶۴ کاشی محاسباتی دارد که ازطریق راهکار شبکه-روی-چیپ (NOC) با یکدیگر ارتباط برقرار میکنند و ازنظر مفهومی تقریباً شبیه Infinity Fabric شرکت AMD هستند. علاوهبراین سختافزار دیگری با عملکرد ثابت وجود دارد که در پردازش لایههای کانولوشن تخصص دارد و با فرآیند ۱۴ نانومتری ساخته شده است. بدین ترتیب شاید IBM فضای بیشتری برای بهبود بازدهی انرژی داشته باشد و برای دستیابی به هدف مذکور باید ابعاد سلولهای آنالوگ را کاهش دهد.

سلولهای حافظهی تغییر فاز، در سرتاسر هریک از ۶۴ کاشی چیدهشده روی نوار متقاطع، توزیع شدهاند که میتوانند فضای ضرب ماتریس-بردار ۲۵۶ در ۲۵۶ را ذخیره کنند. اگر بخواهیم منصفانه به موضوع نگاه کنیم، محدودیتهای عملکردی خاصی در طراحی ترکیبی آنالوگ-دیجیتال وجود دارد. بهعنوان مثال در این روش سیگنالها باید از حالت آنالوگ به دیجیتال و از دیجیتال به آنالوگ تبدیل شوند که هم در نرخ تأخیر پاسخگویی و هم در مصرف انرژی تأثیر دارد. بههرحال این تراشهها در صورت بهینهسازی زمانبندی، درمقایسهبا تراشههای تمام دیجیتال مثل A100 و H100 انویدیا، کارایی بالاتری دارند.

براساس اعلام IBM، ورودی ResNet-9 در طراحی تراشهی هیبریدی این شرکت طی ۱٫۵۲ میکروثانیه پردازش میشود و برای انجام اینکار ۱٫۵۱ میکروژول انرژی مصرف میکند. بهگفتهی ابو سباستین در مرکز IBM Rüschlikon، نسخهی کنونی این تراشه به حداکثر توان عملیاتی ضرب ماتریس-بردار از ۱۶٫۱ تا ۶۳٫۱ تریلیون عملیات درثانیه میرسد.

انقلاب هوش مصنوعی همچنان ادامه دارد و جرقهی اقدامات بزرگ را در بازار محاسبات با توان بالا (HPC) زده است. درحال حاضر نیاز شدید به شتابدهندههای هوش مصنوعی نشان میدهد این بازار همچنان فقط به شرکت انویدیا وابسته است.

تراشههای آنالوگ که موانع راندمان انرژی را از سر راه برمیدارند، قطعاً مورد پذیرش بسیاری از فعالان حوزهی هوش مصنوعی قرار خواهند گرفت اما گسترش این فناوری مثل هر تکنولوژی جدید دیگری به ماندن و رقابت با فناوریهای کنونی بستگی دارد.