پتنت AMD به طراحی چیپلت در پردازنده های گرافیکی اشاره میکند

ای ام دی (AMD) بهتازگی نخستین پتنت مرتبط به پردازندههای گرافیکی دارای طراحی چیپلت (Chiplet) را منتشر کرده است. بهنوشتهی خبرگزاری تکاسپات، پردازندههای گرافیکی مبتنیبر طراحی چیپلت کمکم در حال ظهور هستند؛ بااینحال، فعلا در مراحل اولیه قرار دارند و نمیتوانیم در آیندهی نزدیک، عرضهی رسمی آنها را به بازار شاهد باشیم.

پیشتر، اینتل بارها بهصراحت گفته است به طراحی چیپلت علاقه دارد و از آن در پردازندههای مرکزی و پردازندههای گرافیکی استفاده میکند. براساس اعلام رسمی، نخستین نسل از پردازندههای گرافیکی مجزای اینتل از چیپلت برخوردار خواهد بود.

تاکنون، انویدیا چند مقالهی پژوهشی با محوریت طراحی چیپلت منتشر کرده است؛ اما فعلا جزئیات دقیق کارتهای گرافیک چیپلتمحور این شرکت را نمیدانیم. تا امروز، ای ام دی هیچگاه رسما نگفته بود کارت گرافیک با طراحی چیپلت میسازد؛ ولی پتنت جدید تیم قرمز نشان میدهد این شرکت به استفاده از چیپلت در GPU علاقهمند است.

چیپلتها تراشههایی کوچکتر از تراشههای عادی هستند و پیچیدگی کمتری دارند و بهگونهای طراحی شدهاند تا در همکاری با یکدیگر، درون پردازندههای قدرتمندتر فعالیت کنند. درواقع، پردازندههای دارای طراحی چیپلت از واحدهای پردازشی کوچکتری ساخته شدهاند که هریک از آنها یک چیپلت نامیده میشود.

تحلیلگران میگویند چیپلتها بهاحتمال زیاد آیندهی تمامی قطعات پردازشی قدرتمند را تشکیل میدهند و در مواردی خاص، عملکرد موفقیتآمیزی از خود نشان میدهند. پیشتر، ای ام دی هوشمندانه از طراحی چیپلت در پردازندههای مرکزی استفاده کرده و به نتایج مثبتی رسیده است.

انویدیا و اینتل نیز روی طراحی چیپلت برای پردازندههای گرافیکی کار میکنند

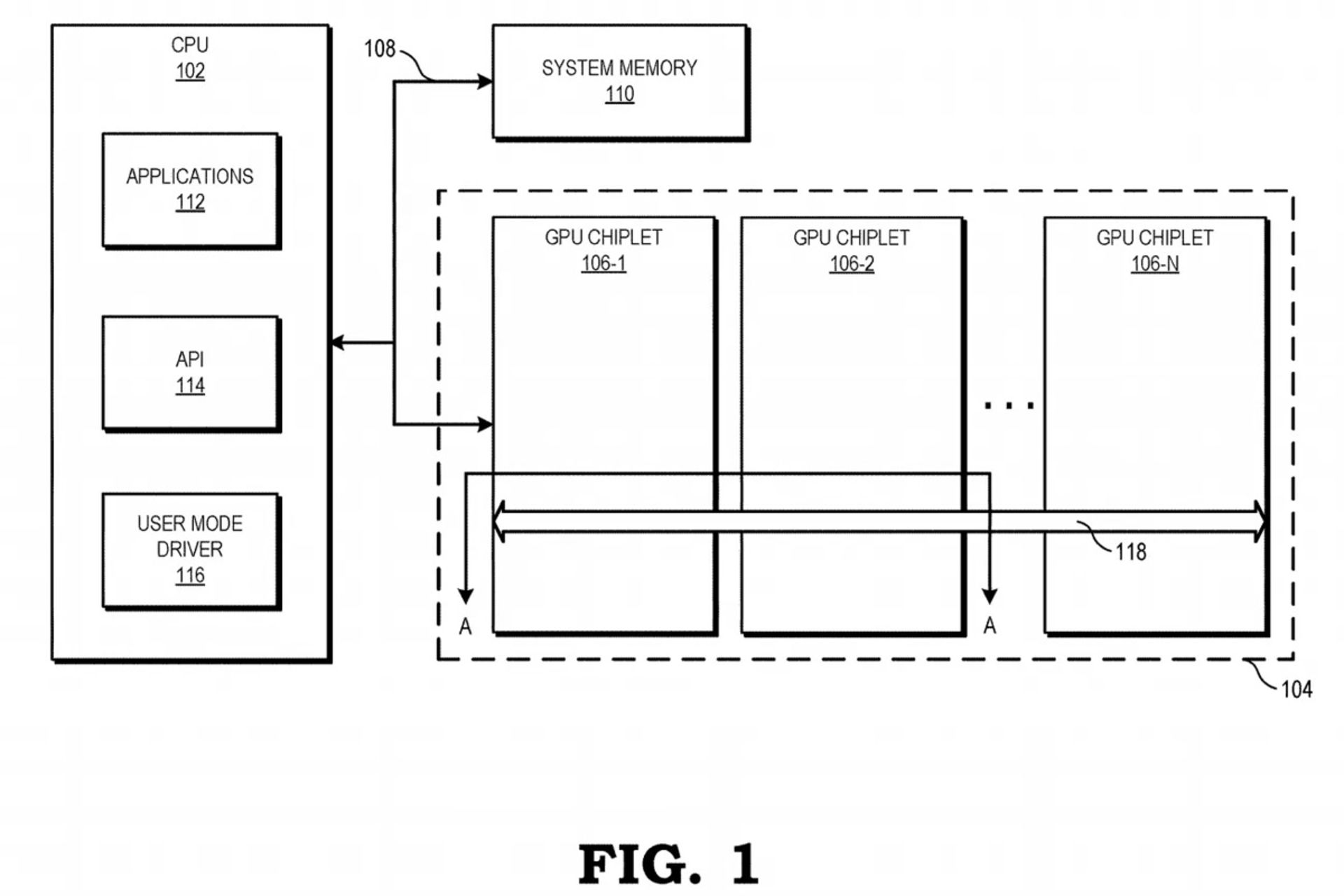

پتنت جدید ای ام دی ۳۱ دسامبر ۲۰۲۰ (۱۱ دی ۱۳۹۹) ثبت شده است و پردازندهای را با طراحی چیپلت نشان میدهد. طراحی چیپلتی که در پتنت ای ام دی میبینیم، شباهت زیادی به طراحی یکپارچه دارد و تحلیلگر تکاسپات میگوید ای ام دی تاحدتوانش تلاش کرده طراحی چیپلت را به طراحی یکپارچه نزدیک کند.

پردازندهی فرضی ای ام دی دو چیپلت مستقل را شامل میشود که با اینترپوزر غیرفعال پرسرعت با نام کراسلینک (Crosslink) بههم متصل شدهاند. اتصال کراسلینک در بین حافظهی کش سطح دوم (L2 Cache) و حافظهی کش سطح سوم (L3 Cache) روی سلسلهمراتب حافظه (Memory Hierarchy) جای میگیرد. تمامی اجزای زیر کراسلینک، نظیر هستههای پردازشی و حافظهی کش L2 و L3 میدانند از چیپلتِ دیگری مجزا هستند که درون پردازنده قرار گرفته است. بهعلاوه، تمامی اجزای بالای کراسلینک، نظیر حافظهی کش L3 و حافظهی GDDR در بین چیپلتها بهاشتراک گذاشته میشوند.

طراحی شرحدادهشدهی ای ام دی مزایای خاصی بههمراه میآورد؛ زیرا در دستهی طراحیهای مرسوم جای میگیرد. ای ام دی ادعا میکند واحدهای پردازشی میتوانند تقریبا با همان سرعتی که با کشهای سطحپایین چیپلت خودشان ارتباط برقرار میکنند، به کش سطحپایین موجود در دیگر چیپلتها دسترسی پیدا کنند. درصورتیکه این ادعا رنگ حقیقت بهخود بگیرد، نرمافزار به بهروزرسانی نیازی نخواهد داشت.

این گفتهها را نمیتوان به طراحی چیپلت شرکتهای اینتل و انویدیا تعمیم داد. برای مثال، اینتل قصد دارد از دو فناوری جدید با نامهای EMIB (پل اتصال چندتراشهایِ توکار) و تجمیع سهبُعدی Foveros استفاده کند. Foveros نوعی اینترپوزر فعال محسوب میشود که از تکنیک TSV (یا Through-Silicon Via) بهره میگیرد. ای ام دی پیشتر بهصراحت گفته است به استفاده از تکنیک TSV تمایلی ندارد. طراحی اینتل به پردازندهی گرافیکی امکان میدهد از حافظهی کشی میزبانی کند که سیستم به آن دسترسی داشته باشد.

انویدیا نیز تاکنون به جزئیات کامل طراحی چیپلت خود اشاره نکرده؛ اما سرنخهایی دردسترس قرار داده است که توجه به آنها میتواند ما را به نتایجی برساند. مقالهی پژوهشی انویدیا در سال ۲۰۱۷ به طراحی ویژهای با چهار چیپلت مجزا با فناوری NUMA (دسترسی غیریکنواخت به حافظه) اشاره میکند. همچنین، انویدیا پیشتر روی حافظهی کش جدید سطح یکونیم (L1.5 Cache) کار کرده است که بهطوراختصاصی امکان دسترسی به دادههای دور را از بین میبرد. طراحی چیپلت ای ام دی ممکن است در نگاه اول در حدواندازهی طراحیهای اینتل و انویدیا جذاب نباشد؛ اما آنچه ای ام دی شرح داده، عملی بهنظر میرسد. درادامه، تصویری دیگر از پتنت ای ام دی را مشاهده میکنید.

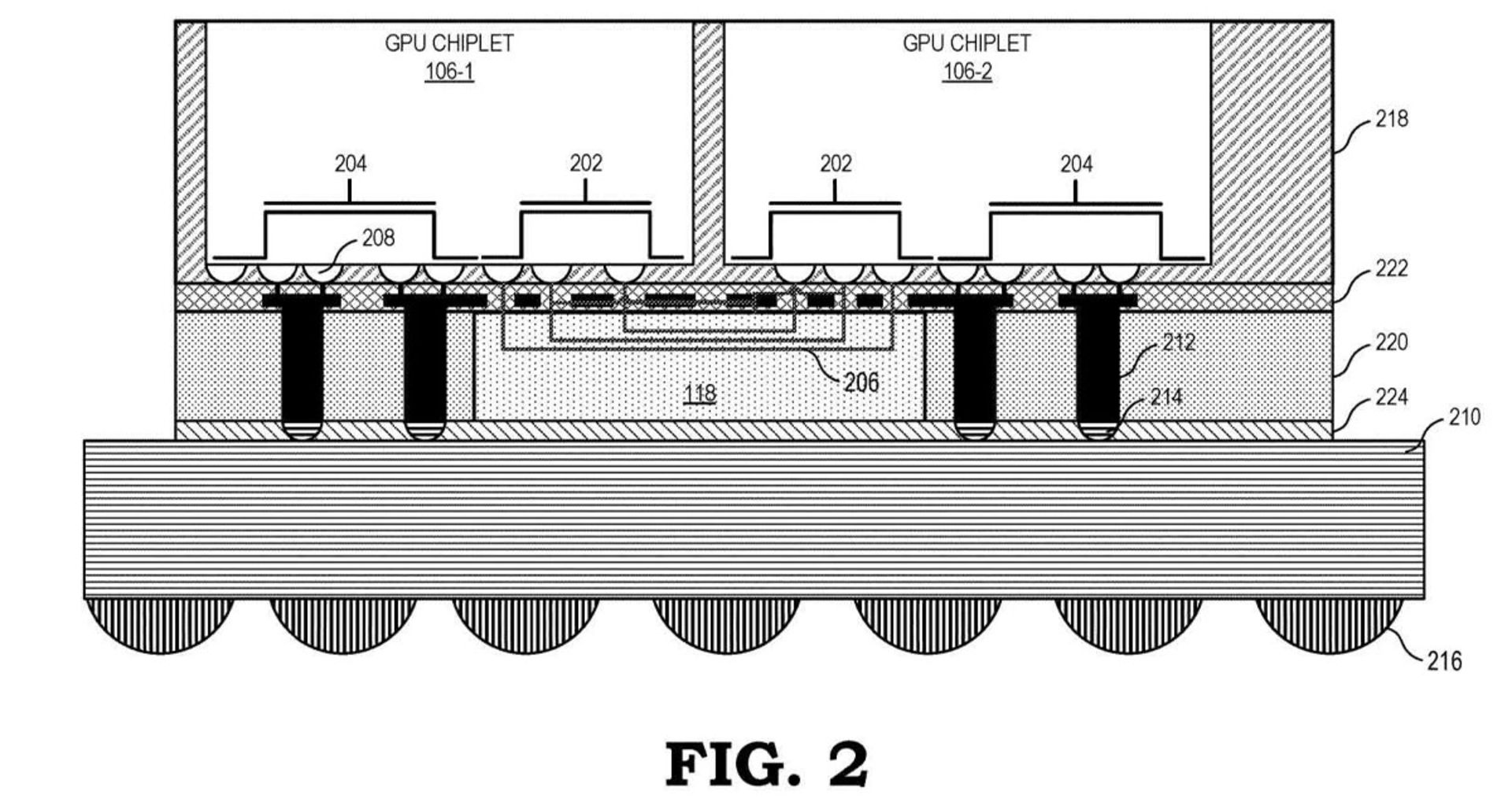

تصویری که در بالا میبینید، نمای سطح مقطع طراحی ای ام دی را نشان میدهد و دو چیپلت روی برد مدار را شامل میشود. دو چیپلت مذکور که در تصویر بالا با اعداد ۱-۱۰۶ و ۲-۱۰۶ مشخص شدهاند، بهصورت عمودی روی کراسلینک غیرفعال (۱۱۸) قرار داده شدهاند و بهمنظور دسترسی به کراسلینک، از ساختارهای رسانای اختصاصی بهره میبرند (۲۰۶) و درنهایت، با یکدیگر ارتباط برقرار میکنند. ساختارهای رسانای مذکور در پتنت ای ام دی که به کراسلینک متصل نیستند (۲۰۴)، برای دریافت انرژی و انجام کارهای دیگر به برد مدار متصل میشوند.

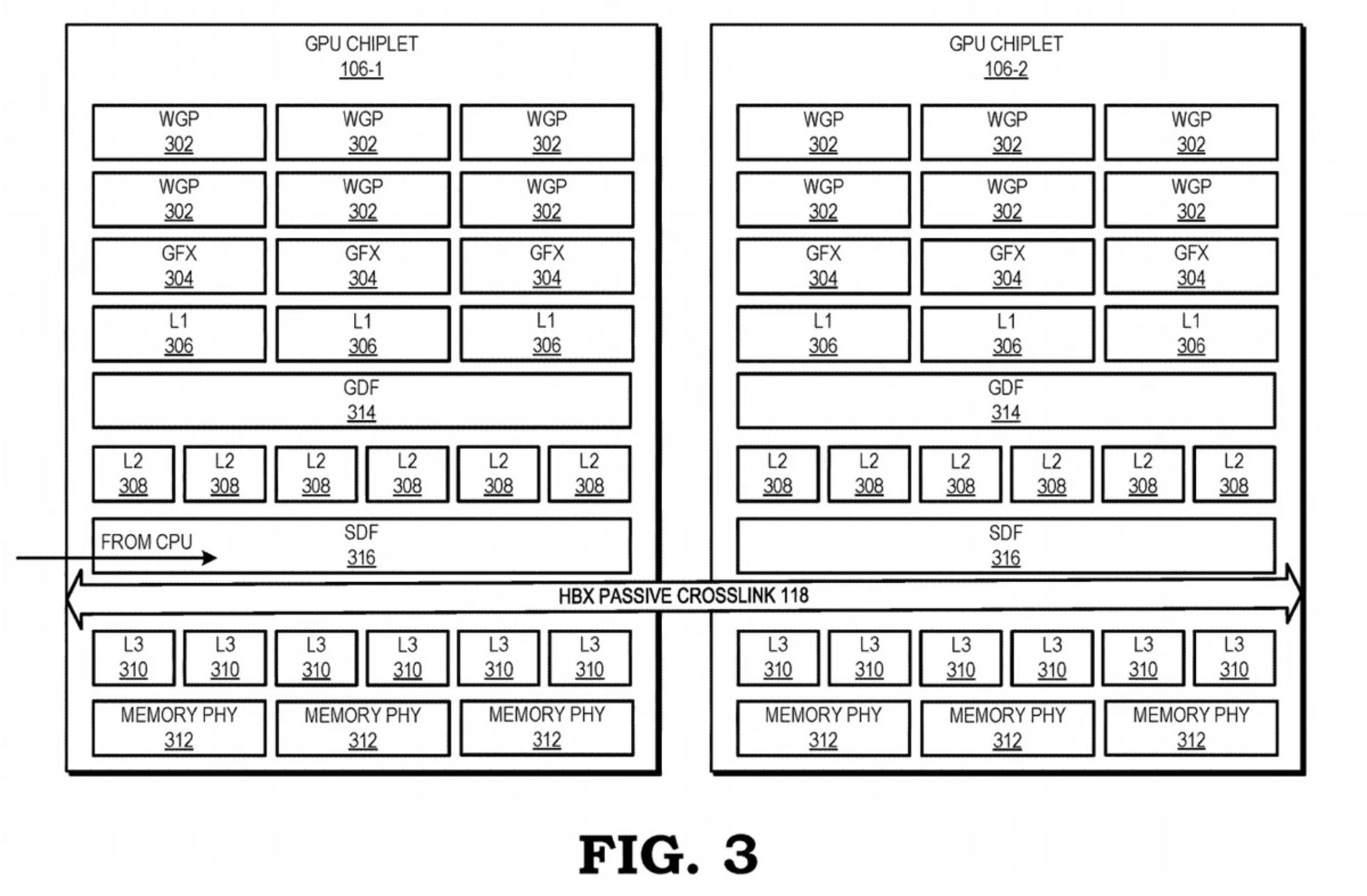

تصویر بالا سلسلهمراتب حافظهی کش را بهتصویر میکشد. واحدهای WGP (پردازندههای گروه کاری) که با عدد ۳۰۲ در تصویر بالا مشخص شدهاند و مجموعهای از هستههای سایهزن محسوب میشوند، بههمراه واحدهای GFX (عملکرد ثابت) که با عدد ۳۰۴ در تصویر بالا دیده میشوند. واحدهای GFX مستقیما به حافظهی کش L1 کانال متصل میشوند (۳۰۶) و پردازندههایی مستقل برای هدفی خاص هستند.

در طراحی ای ام دی، هر چیپلت چندین محفظهی کش L2 را شامل میشود (۳۰۸) که میتوان جداگانه به آنها دسترسی پیدا کرد و حافظههای کش L2 صرفا با همان چیپلت ارتباط دارند. در هرکدام از چیپلتها، چندین محفظهی حافظهی کش L3 هم دیده میشود (۳۱۰) که با کل پردازندهی گرافیکی در ارتباط هستند.

واحد GDF (قطعهی مربوط به دادههای گرافیکی) که با عدد ۳۱۴ در تصویر بالا دیده میشود، محفظههای حافظهی کش L1 را به محفظههای حافظهی کش L2 متصل میکند. همچنین، واحد SDF (قطعهی مربوط به دادههای مقیاسپذیر) محفظههای کش L2 را ترکیب و آنها را به کراسلینک متصل میکند (۱۱۸). کراسلینک به واحد SDF و محفظههای کش L3 در تمامی چیپلتها اتصال پیدا میکند. لاینهای حافظهی GDDR که با نام Memory PHY در تصویر بالا معرفی شدهاند (۳۱۲)، به محفظههای کش L3 متصل میشوند.

ای ام دی برای تشریح نحوهی کار قطعات مثالی زده است: اگر یک واحد WGP در یکی از چیپلتها بخواهد از محفظهی GDDR در چیپلت دیگر داده دریافت کند، این داده از محفظهی کش L3 عبور میکند، ازطریق کراسلینک به واحد SDF میرسد، به محفظهی کش L2 ارسال میشود و درنهایت با عبور از واحد GDF، به محفظهی کش L1 وارد میشود.

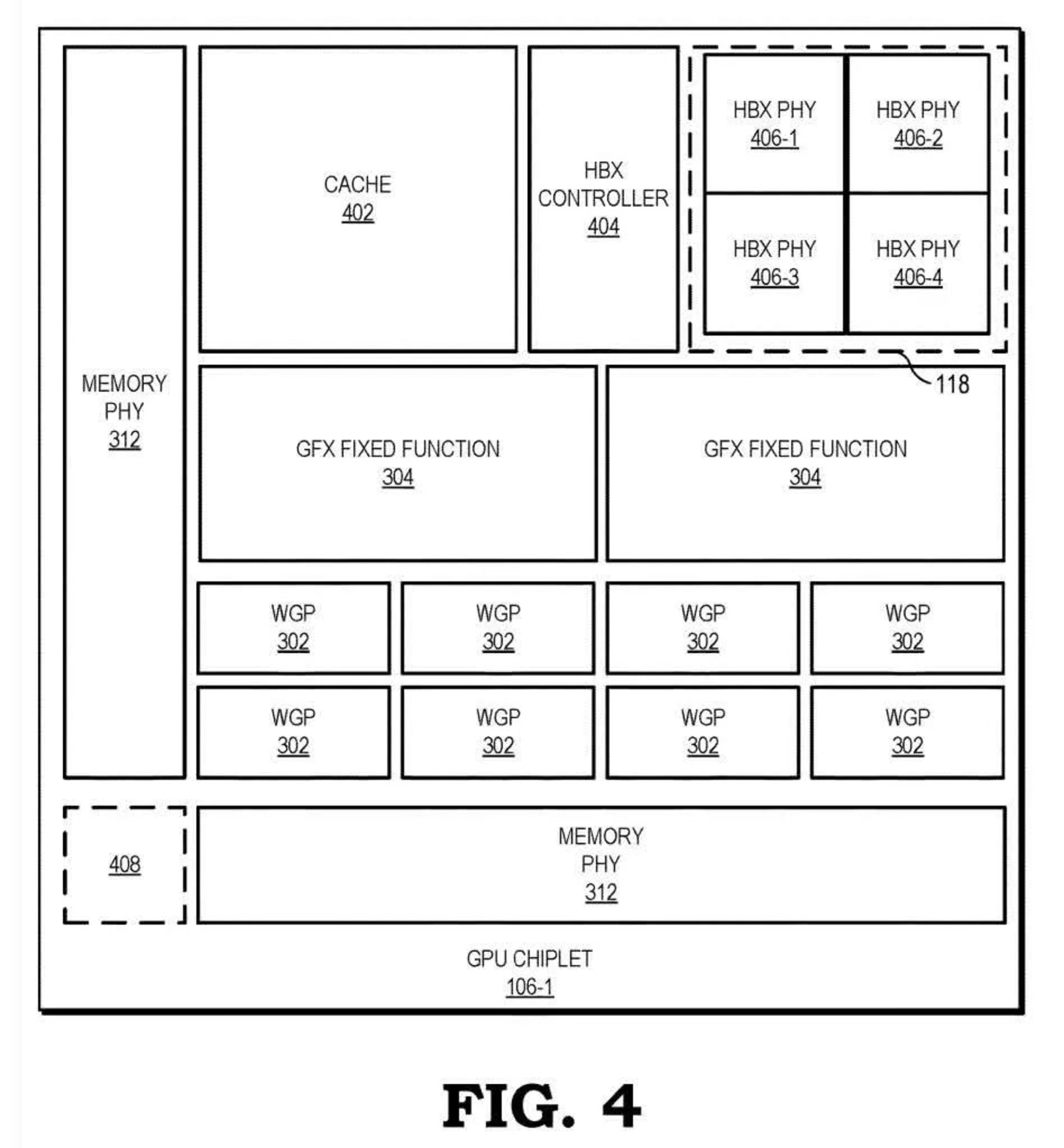

تصویر بالا نیز نمایی از بالای طراحی چیپلت ای ام دی را نشان میدهد. در این طراحی، مکان احتمالی هریک از قطعات پردازشی و ابعاد آنها را دقیقتر میبینیم. کنترلر HBX که با عدد ۴۰۴ مشخص شده است، وظیفهی مدیریت کراسلینک را برعهده دارد. این نکته را نیز مدنظر قرار دهید که چیپلت ازطریق ساختارهای رسانای HBX PHY به کراسلینک متصل میشود که با عدد ۴۰۶ مشخص شدهاند. مربع کوچکی که در بخش پایین سمت چپ تصویر میبینید (۴۰۸)، احتمالا رابطی اضافی به کراسلینک است تا امکان اتصال چیپلتهای بیشتر به آن فراهم شود.

دیدگاه شما کاربران زومیت دربارهی پتنت جدید ای ام دی چیست؟

نظرات