اینتل با فناوری EMIB، پهنای باند فوقالعادهای برای شتاب دهنده Stratix 10 MX به ارمغان میآورد

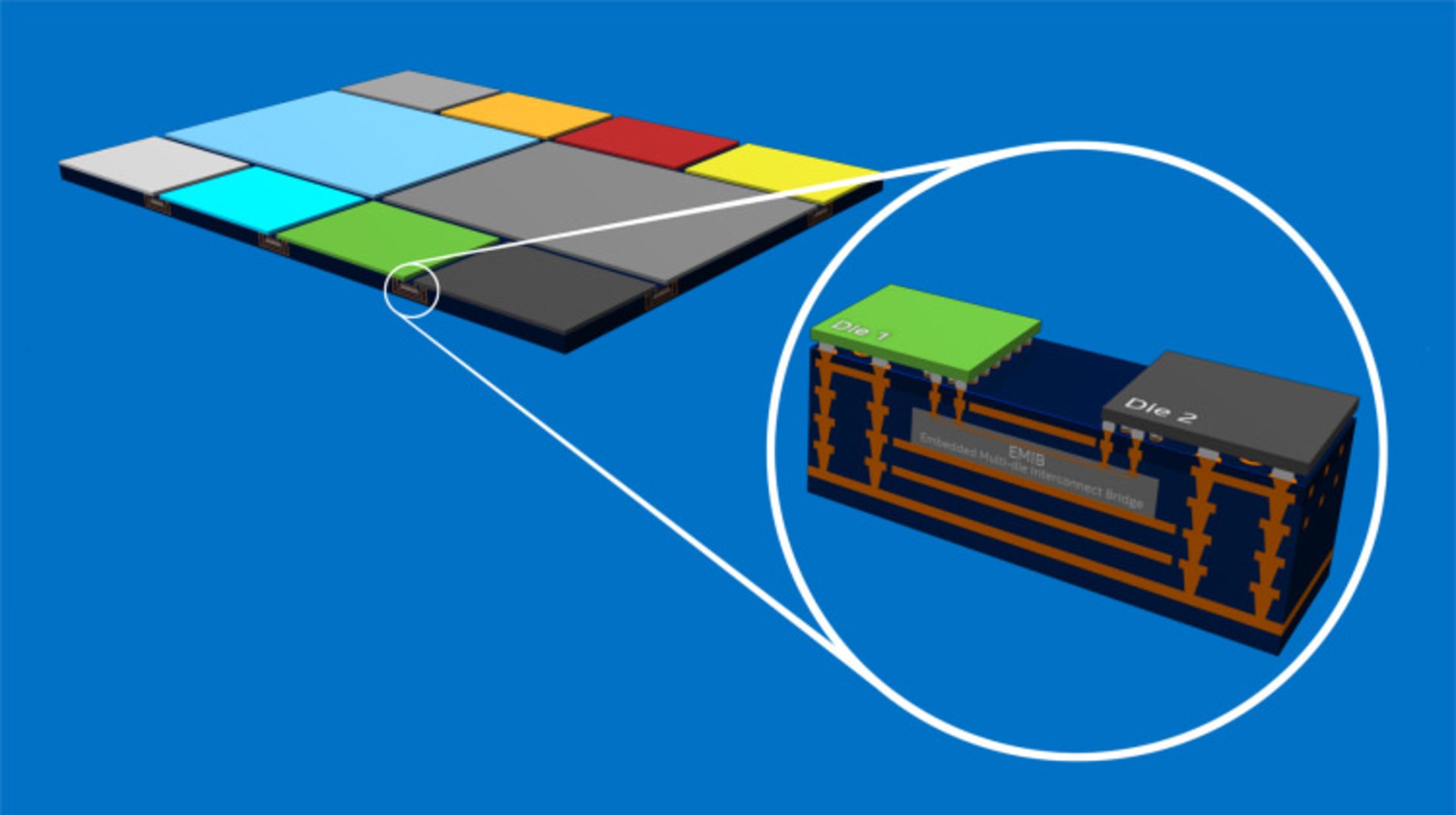

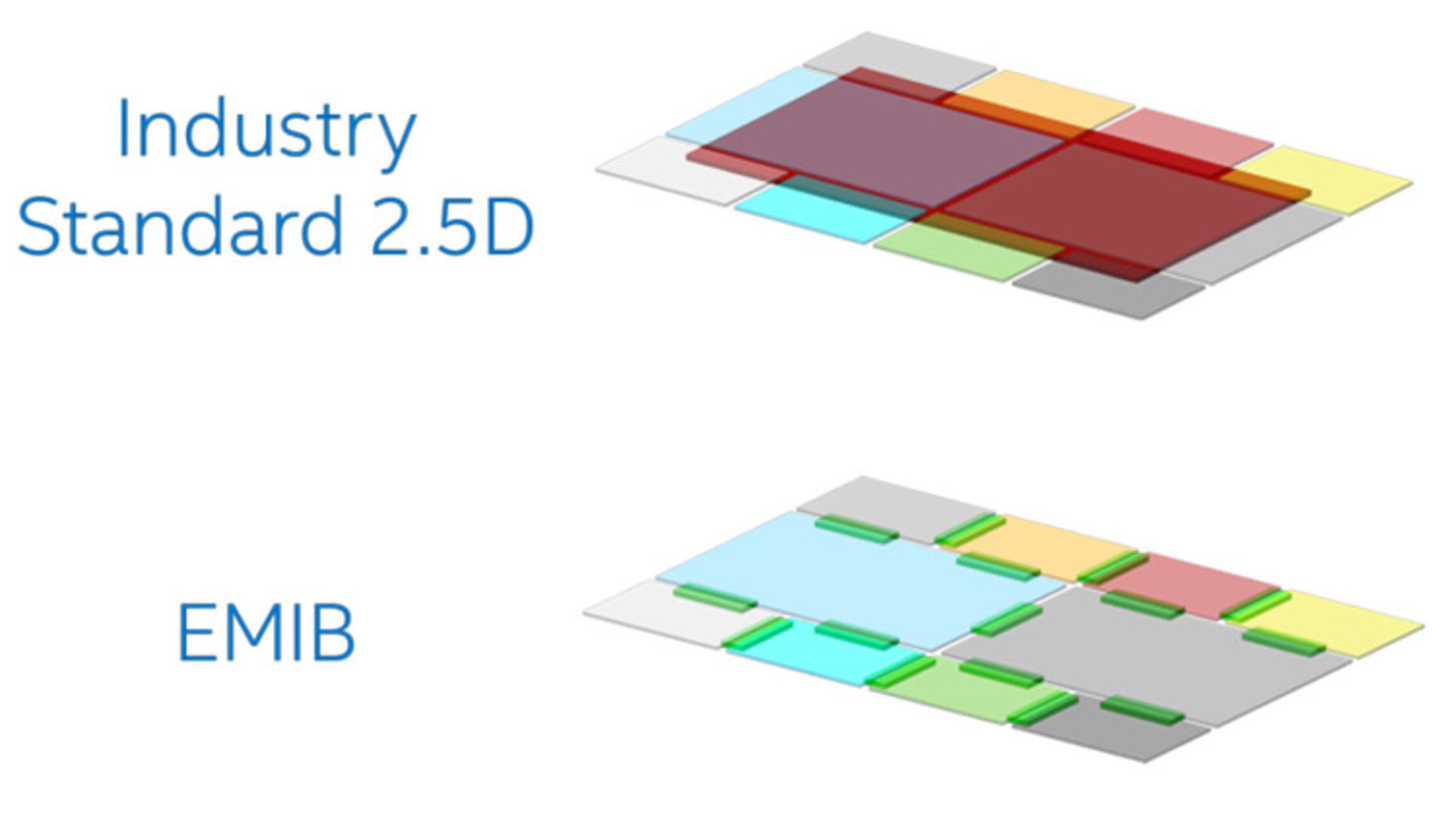

فناوری پل اتصال (مونتاژ) چندگانهی جاسازی شده که به اختصار EMIB نامیده میشود، یکی از جالبترین تحولات در طراحی سطح بستهبندی در سال جدید به شمار میرود. شرکت اینتل توسعهی فناوری EMIB را برعهده داشته است. این برشهای کوچک سیلیکونی امکان اتصال غیر یکنواخت قطعات کوچک موسوم به Dice را بدون استفاده از رابطهای بزرگ (Interposer) در بستر یکسان به اینتل میدهند. زومیت را همراهی کنید.

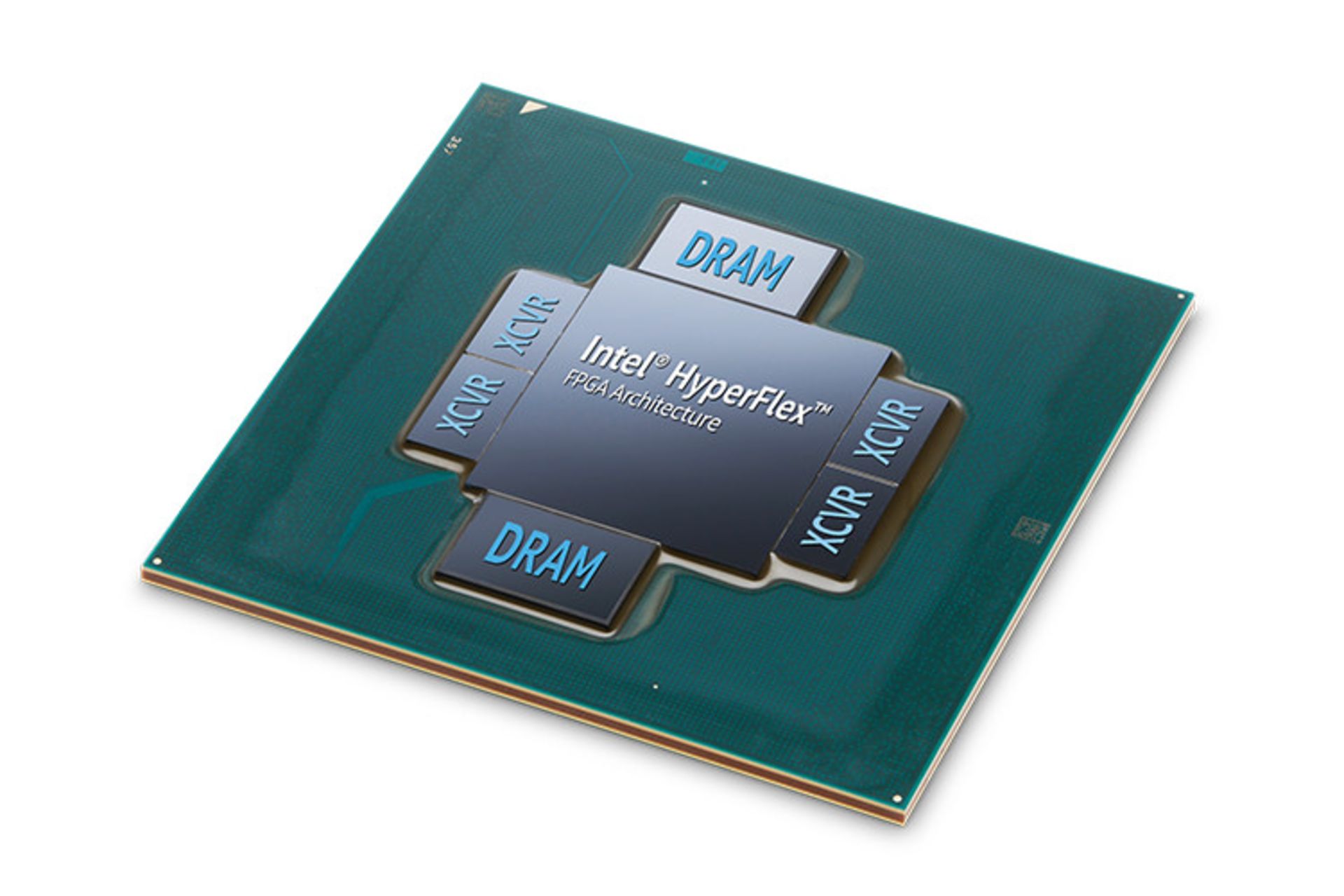

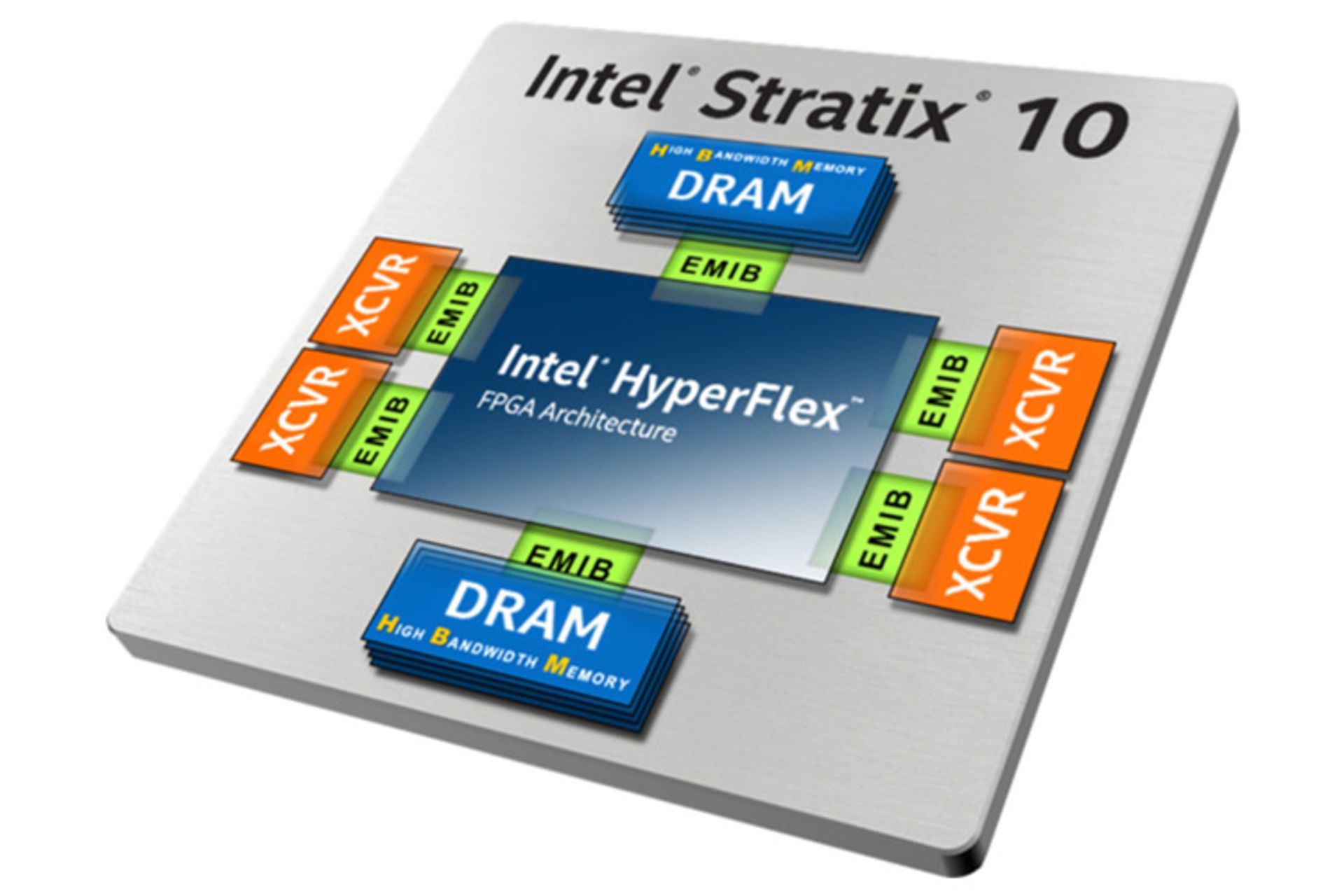

اینتل امروز چگونگی پشت سر گذاشتن چالش تغذیهی شتابدهندهها با پهنای باند حافظهی کافی با استفاده از EMIB را که بخشی از خانوادهی جدید Stratix 10 MX family تراشههای FPGA است، به نمایش گذاشت. مشابه با حافظهی رم روی برد HBM2 به کار بردهشده در پردازندهی مشترک اینتل و گرافیک رادئون AMD، شرکت اینتل از باند ارتباطی EMIB که مخفف عبارت «Embedded Multi Die Interconnected Bridge» است، برای ایجاد ارتباط بین تراشههای FPGA شتابدهندهی Stratix 10 MX به ۴ کاشی حافظهی رم با پهنای باند بالا (HBM2) بهره میبرد تا به مجموعه پهنای باند شگفتآور ۵۱۲ گیگابایت بر ثانیه دست پیدا کند. تمامی این کارها به خاطر جلوگیری از ایجاد گلوگاه برای حافظهی پردازنده است. در کنار دستههای حافظهی HBM2، اینتل همچنین از EMIB برای اتصال ۴ ترانسیور (فرستنده و گیرنده) به کالبد FPGA بهمنظور دریافت یا ارسال سیگنالهایی مانند PCIe بهره میبرد.

اینتل در فایل اختصاصی مربوط به FPGA، چالشهای پیش روی افزایش سرعت به نسبت ثابت معماریهای سطح سیستم حال حاضر را با استفاده از FPGA و حافظهی رم DDR4 تشریح کرده است. طبق توضیحات رسمی اینتل، ۳ کانال حافظهی رم DDR4 با فرکانس ۳۲۰۰ مگاهرتز قادر به فراهم کردن یکی از FPGA-های امروزی با پهنای باند ۸۰ گیگابایت بر ثانیه هستند؛ اما مقیاسگذاری آن، باعث شکلگیری چالش چیدمان و طراحی حالاتی میشود که غلبه کردن بر آن با استفاده از معماریهای سیستم کنونی، غیر ممکن به نظر میرسد. نظر به اینکه تقاضا برای پردازشهای FPGA در حال افزایش است، اینتل اظهار میکند که دیگر قرار دادن پینهای ورودی و خروجی DDR در یک بسته برای افزایش پهنای باند مورد نیاز برنامههای کاربردی بهراحتی امکانپذیر نخواهد بود.

حتی اگر قرار دادن پینهای ورودی و خروجی کافی در یک بستهی FPGA ممکن باشد، اینتل ادعا میکند که حافظهی اضافه نیازمند صدها رد الکترونی طویل به ازای شکاف DIMM با مصرف انرژی بالای بافرهای ورودی و خروجی برای مدیریت آن خواهد بود. این امر سبب افزایش تقاضای توان از پهنای باند میشود و محدودیتهای طراحی واقع بینانه را در بازار مرکز داده با حساسیت عملکرد در هر وات افزایش میدهد. در نهایت، این شرکت اظهار میکند که جای دادن ۱۰ عدد DIMM از نوع DDR4 در یک برد مدار چاپی (PCB) برای دستیابی به توان عملیاتی نظری ۲۵۶ گیگابایت بر ثانیه، بهواقع فضای بسیار زیادی میگیرد و به چگالی محاسبهی پایگاه داده صدمه وارد میکند.

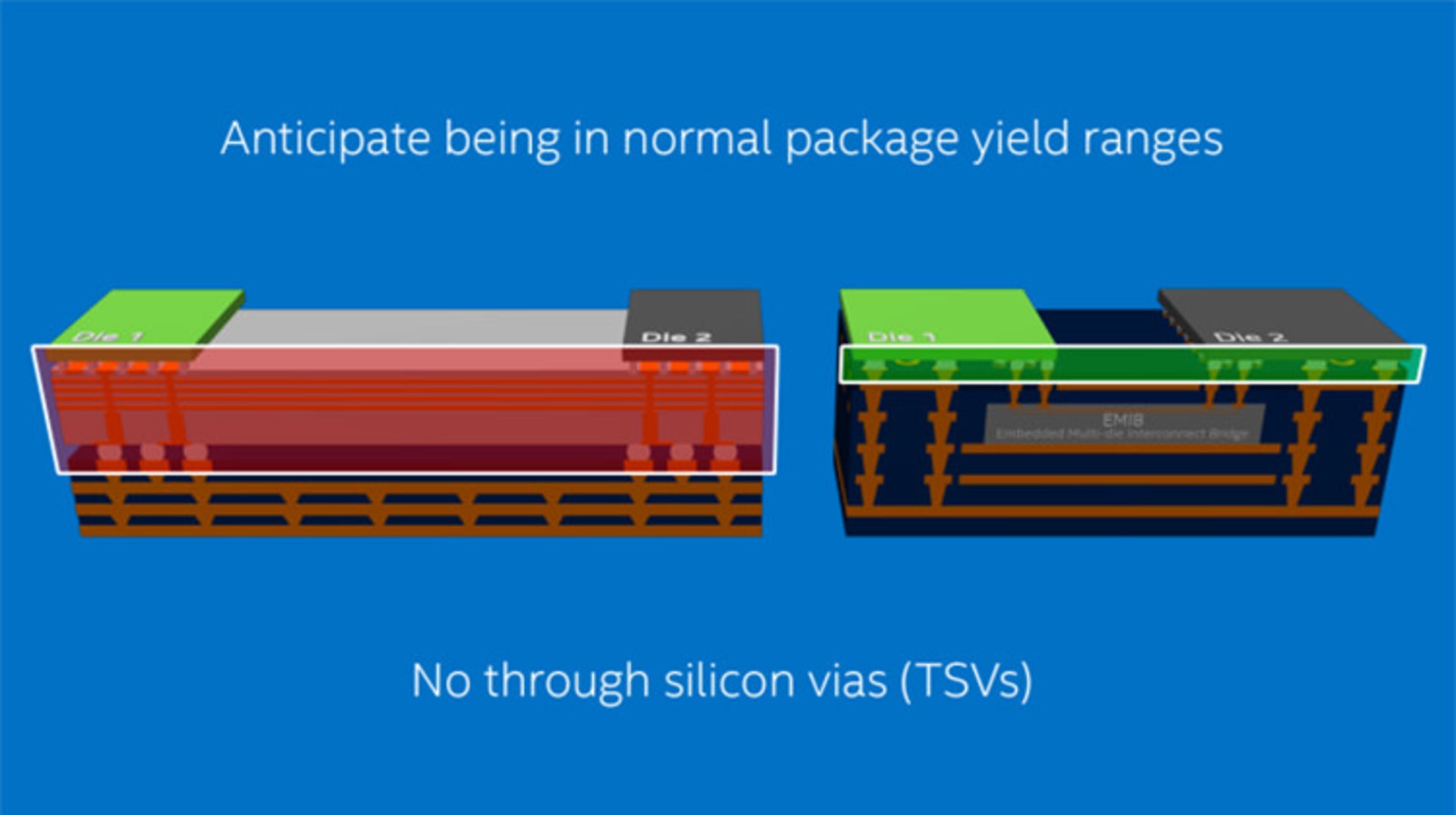

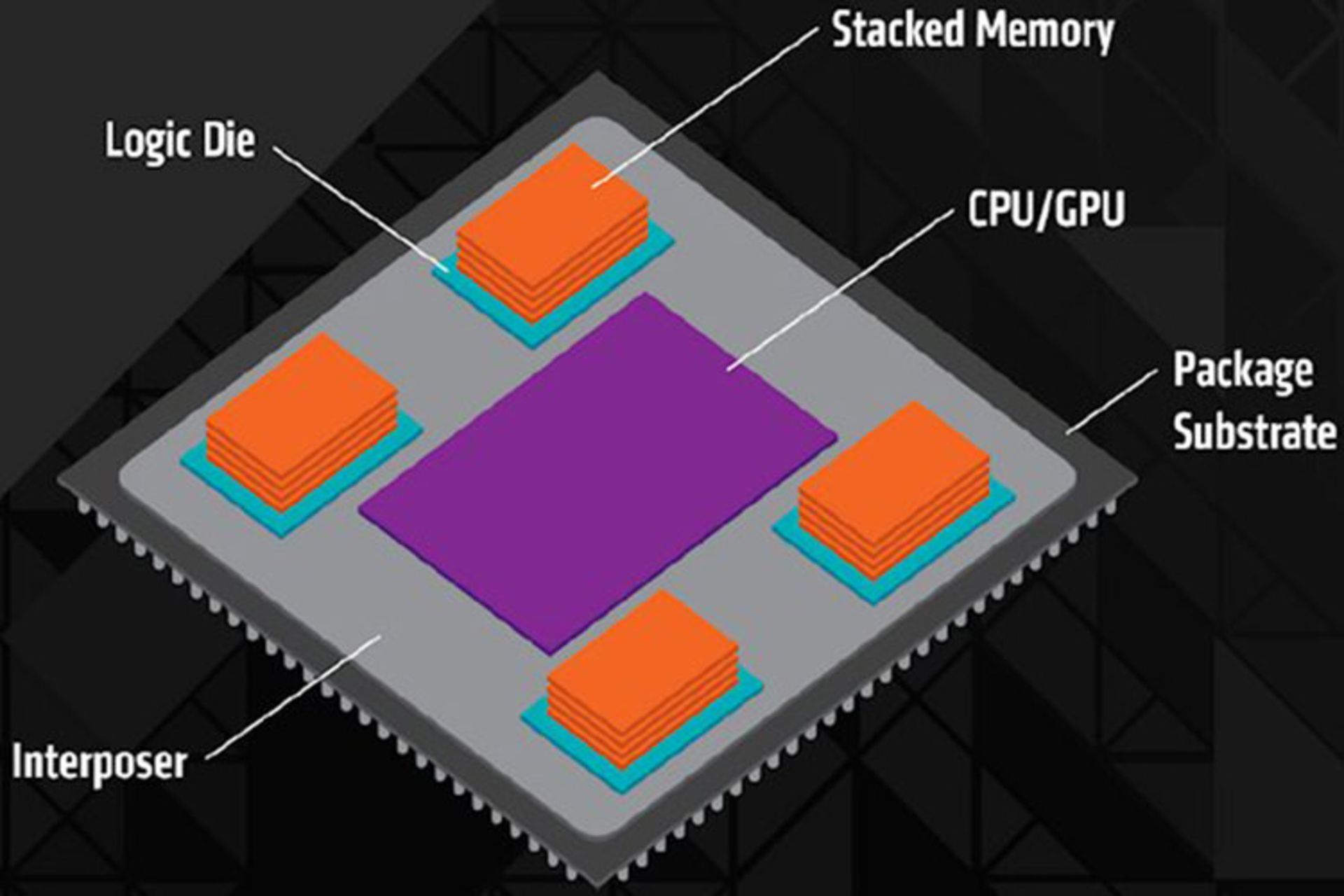

تمامی این نگرانیها خبر از محدودیتهایی میدهد که حتی موجب شده است AMD شروع به توسعهی حافظهی رم HBM برای پردازندههای گرافیکی اختصاصی خود کند. حافظهی HBM برای مرتفع کردن مشکل اشغال بخش بزرگی از برد مدار چاپی به وسیلهی تعداد در حال رشد تراشههای حافظهی GDDR5 و سیمهای مورد نیاز برای ایجاد ارتباط و توانرسانی به آنها توسعه داده شده است. این موضوع باعث نمیشود که HBM مقدار بسیار زیادی از پهنای باند خام را برای بوت شدن فراهم کند. در نظر بگیرید که بسیاری از پیادهسازیهای جاری HBM و HBM2 نیازمند ساخت یک رابط میانجی برای اتصال تراشههای حافظه با واحد پردازش گرافیکی (GPU) هستند؛ تکهای بزرگ از سیلیکون اضافه که با در نظر گرفتن حجم دستههای رم و محدودیت اندازهی کلی تراشه، به پیچیدگی بستهبندی منجر میشود.

اینتل EMIB-های خود را بهعنوان یک راهکار ایدهآل برای برطرف کردن چالشهای متصل شدن FPGA-ها با DDR4 برای افزایش پهنای باند ارائه داده است. برخلاف رابط میانجی سیلیکونی که حافظهی رم HBM را با FPGA و واحدهای پردازش مرکزی وگا پیوند میدهد، EMIB-ها اجازه میدهند که اینتل اتصالهای حافظهی HBM2 را بدون گرفتار شدن در محدودیتهای اندازهی تراشههای بستهبندیشده روی سیلیکون رابطهای میانجی، با FPGA-های شتابدهندهی Stratix 10 MX پیوند دهد. اینتل همچنین ادعا میکند که استفاده از EMIB باعث میشود که از بازده بستهی مشابه با بسترهای بدون EMIB هم بهرهمند باشد. پل یک قطعهی کوچک سیلیکونی است که به جای TSV رابطهای میانجی، از برآمدگیهای کوچکی برای اتصال استفاده میکند؛ به همین دلیل لزومی برای نگرانی در مورد هیچ کدام از چالشهای ساخت بالقوه و کاهش بازده TSV نخواهد بود. TSV یک اتصال الکتریکی عمودی است که بهطور کامل از سراسر ویفر یا اتصال سیلیکونی عبور میکند. در عوض میتوان با استفاده از فنون تراشهی واگرد (Flip chip) تراشههای معین شده برای ادغام EMIB را بستهبندی کند. یک تراشهی واگرد، تراشهی نیمه رسانایی است که تمام نوک آن در یک طرف به شکل بالشتکهای لحیمی یا برآمدگیهای اتصالی قرار دارند. بعد از حفاظت و پرداخت سطح تراشه، آن را بهصورت وارونه روی بستر قرار میدهند؛ بهطوری که اتصالات داخلی و قطعات پوستهی نازک یادشده قبلاً روی آن نشانده شده است. سپس با اعمال گرما یا ترکیبی از فشار و انرژی فراصوتی، تمام اتصالها بهصورت همزمان ایجاد میشوند.

در نهایت تمامی این فناوریها اجازه میدهند که FPGA-های شتابدهندهی Stratix 10 MX از افزایش پهنای باندی بهرهمند باشد که بستهی بسیار فشردهتری از FPGA متصل به حافظهی DDR دارد. به علاوه، معماری چندکانالهی HBM2 اجازه میدهد که این FPGA-ها بهصورت همزمان در یک مرتبه از عملیات، دسترسیهای بیشتری به حافظه داشته باشند. در مقایسه با ۴ الی ۶ کانال حافظهی DDR معمولی، در پیادهسازی FPGA امروزی تعداد آن حداکثر میتواند به ۶۴ برسد. پردازندهی Stratix 10 MX FPGA با استفاده از معماری FPGA هایپرفلکس (HyperFlex FPGA) ساخته شده و قادر به اجرا شدن در سرعت کلاک حداکثری ۱ گیگاهرتزی است. اینتل اظهار میکند که بهبودهای صورتگرفته، در کاربردهایی که میتوانند شتاب داده شوند، امکان ارائهی عملکرد بالا و انعطافپذیری بیشتری برای تراشههای Stratix 10 MX فراهم میکند.

اینتل در ادامهی اظهارات خود، افزایش پهنای باند شتابدهندههای Stratix 10 MX را برای طیف گستردهای از محاسبات با کارایی بالا، پردازش تصویر با وضوح بالا، شبکههای کابلی، تجزیه و تحلیل دادهها و کاربردهای اینترنت اشیاء در مرکز داده، ایدهآل دانست.

پیشرفت شتابدهندهی Stratix 10 MX را چگونه ارزیابی میکنید؟

نظرات