ترانزیستورهای نسل بعد نانوصفحات خواهند بود

ریزپردازندههای مدرن از پیچیدهترین سیستمهای بهکاررفته در دستگاههای جهان هستند که در قلب آنها، بخشی بسیار ساده و زیبا بهنام ترانزیستور وجود دارد. امروزه، میلیاردها ترانزیستور در ریزپردازندهها وجود دارد که تقریبا همهی آنها ساختاری مشابه هم دارند. بهبود کارایی و افزایش تراکم این ترانزیستورها سادهترین راه برای افزایش عملکرد ریزپردازندهها و رایانههایی است که ریزپردازندهها به آنها نیرو میدهند.

این افزایش تراکم پایه و اساس قانون مور است. این قانون بیان میکند تعداد ترانزیستورهای روی یک تراشه با مساحت ثابت، هر دو سال تقریبا دوبرابر میشود؛ حتی اکنون که دیگر این قانون بهسختی اجراشدنی است. باوجوداین مشاهده میشود ساختن ترانزیستورهای کوچکتر و بهتر برای ریزپردازندهها بدون درنظرگرفتن هزینهی سرسامآور ساخت این تراشهها سختتر شده است. کاستن از اندازهی این ترانزیستورها در چنین ابعادی، نیازمند امکاناتی است که فقط شرکتهای اینتل و سامسونگ و صنایع نیمههادی تایوان (TSMC) از آن برخوردار و درحالحاضر در حال تولید مدارهای مجتمع (IC) با لیتوگرافی هفت نانومتری هستند.

هفت نانومتری بودن ساختار ترانزیستورها مفهوم فیزیکی خاصی ندارد و فقط مقیاسی برای نشاندادن میزان کوچکشدگی دستگاههای موجود در مدارهای مجتمع است. این سبک از نامگذاری از دوران کشف قانون مور مرسوم بود.

درحالحاضر، معماری پردازندهها با لیتوگرافی هفت نانومتری، جدیدترین فناوری بهکاررفته در این صنعت است؛ اما سامسونگ و TSMC در آوریل سال جاری اعلام کردند کار روی پردازندههای خود با لیتوگرافی پنج نانومتری را آغاز کردهاند. البته، سامسونگ پا را از این فراتر گذاشته و تصمیم گرفته است با کنارگذاشتن سنتها در تولید پردازنده در یک دههی اخیر، پردازندههای جدیدی را از سال ۲۰۲۰ با لیتوگرافی سه نانومتری و تکیه بر طراحی جدید بهصورتی محدود تولید و روانهی بازار کند.

به ترانزیستورهای جدید القاب مختلفی از قبیل دروازهی همهطرفه و کانال چندوجهی و نانوبام داده شده است؛ اما در مراکز تحقیقاتی، به آنها صفحات نانو میگویند. نحوهی نامگذاری این ترانزیستورها نکتهی چندان مهمی نیست؛ بلکه موضوع مهم این است که طرح بهکاررفته در این دست از ترانزیستورها، امکان دارد طراحی نهایی در ساختار تمامی ترانزیستورها بعد از این برههی زمانی باشد. قطعا تغییراتی جزئی در ساختار ترانریستورهای نسل بعدی ایجاد خواهد شد؛ اما روش اصلی ساخت همان نانوصفحات خواهند بود.

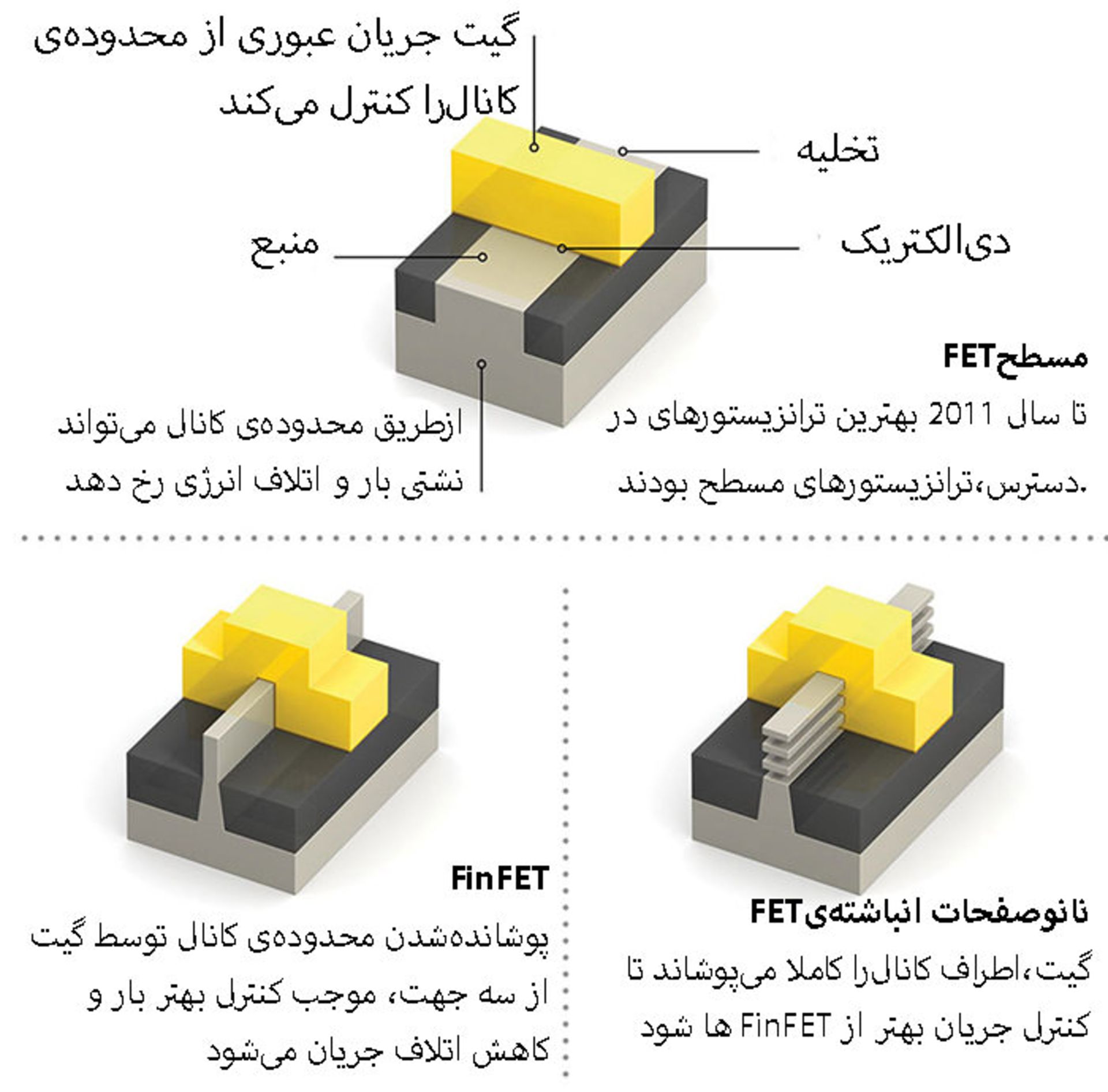

شکل و مواد بهکاررفته در ساختار ترانزیستورها با گذر زمان تغییر کرده است؛ اما ترانزیستورهای اثر میدانی نیمهرسانای اکسید فلز (MOSFET) که در ریزپردازندهها استفاده میشوند، از زمان اختراع در سال ۱۹۵۹، همان ساختار پایه را دارند و همگی شامل پشتهی دروازه، ناحیهی کانال، الکترود منبع و الکترود تخلیه هستند. در شکل اصلی ترانزیستور، منبع و تخلیه و کانال از جنس سیلیسیم ناخالص هستند و ساختار این ناخالصیها اتمهای عناصر دیگر را شامل میشود تا منطقهای با بار منفی سیّار زیاد (نوع n) یا منطقهای با بار مثبت سیّار زیاد (نوع p) بهوجود آورد. البته، فناوری CMOS (ترکیب بنیادی در ساخت مدارهای مجتمع) که در تراشههای رایانههای امروزی کاربرد دارد، نیازمند هر دو نوع پیوند n و p از ترانزیستور است.

پشتهی دروازه در MOSFET درست در بالای ناحیهی کانال قرار دارد. در تراشههای امروزی، پشتهی دروازه از فلزی برای الکترود دروازه ساخته میشود که روی لایهای از مواد دیالکتریک، نوعی عایق قطبیدهشده، قرار گرفته است تا میدان الکتریکی در ناحیهی کانال ترانزیستور ایجاد و از نشت بار جلوگیری شود. با اعمال ولتاژ زیاد در مقایسه با ولتاژ منبع روی دروازه، لایهای از حاملهای بار سیّار در نزدیکی رابط میان دیالکتریک و سیلیسیم ایجاد میشود و با کاهش ولتاژ دروازه تا نزدیکی عدد صفر، مسیر رسانا تقریبا بسته و ترانزیستور خاموش میشود.

ابتدا به ولتاژی قوی احتیاج داریم تا جریان را ازطریق کانال از منبع به تخلیه برساند. ازآنجاکه ساختار ترانزیستورها روزبهروز کوچکتر میشود، آثار این ولتاژ قوی درنهایت به بزرگترین تغییرشکل در تاریخ ترانزیستور منجر خواهد شد. دلیل صحت این گفته آن است که ولتاژ اعمالشده میتواند ناحیهای رسانا بین الکترودها ایجاد کند و هرچه قسمت مربوطبه کانال با معرفی نسل جدید ترانزیستور کوتاهتر میشود، تأثیر تخلیه ولتاژ بیشتر میشود. همچنین، بار میتواند از زیر منطقهی نزدیک به دروازه نشت کند؛ درنتیجه ترانزیستور هرگز خاموش نمیشود و باعث اتلاف برق و تولید گرما میشود.

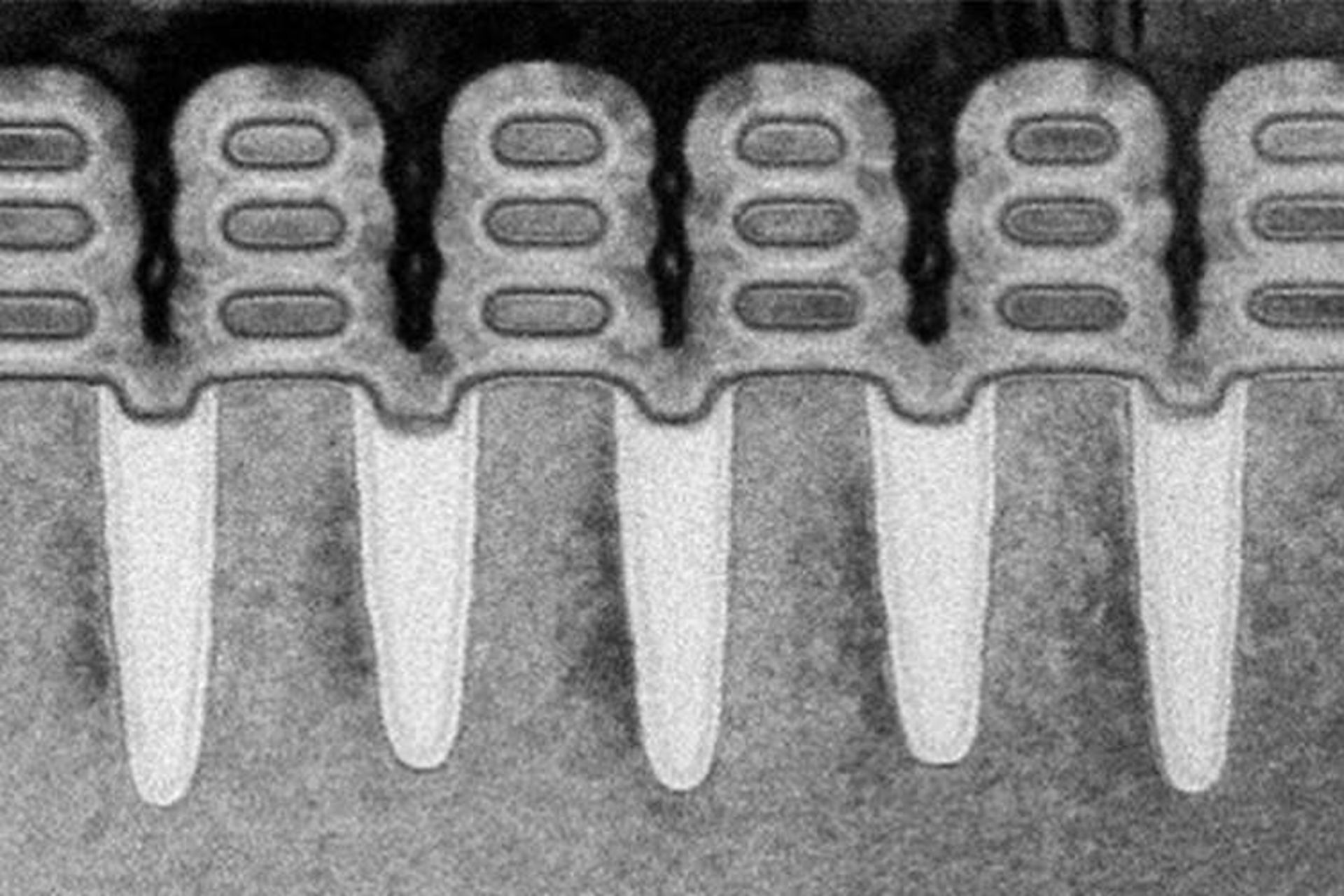

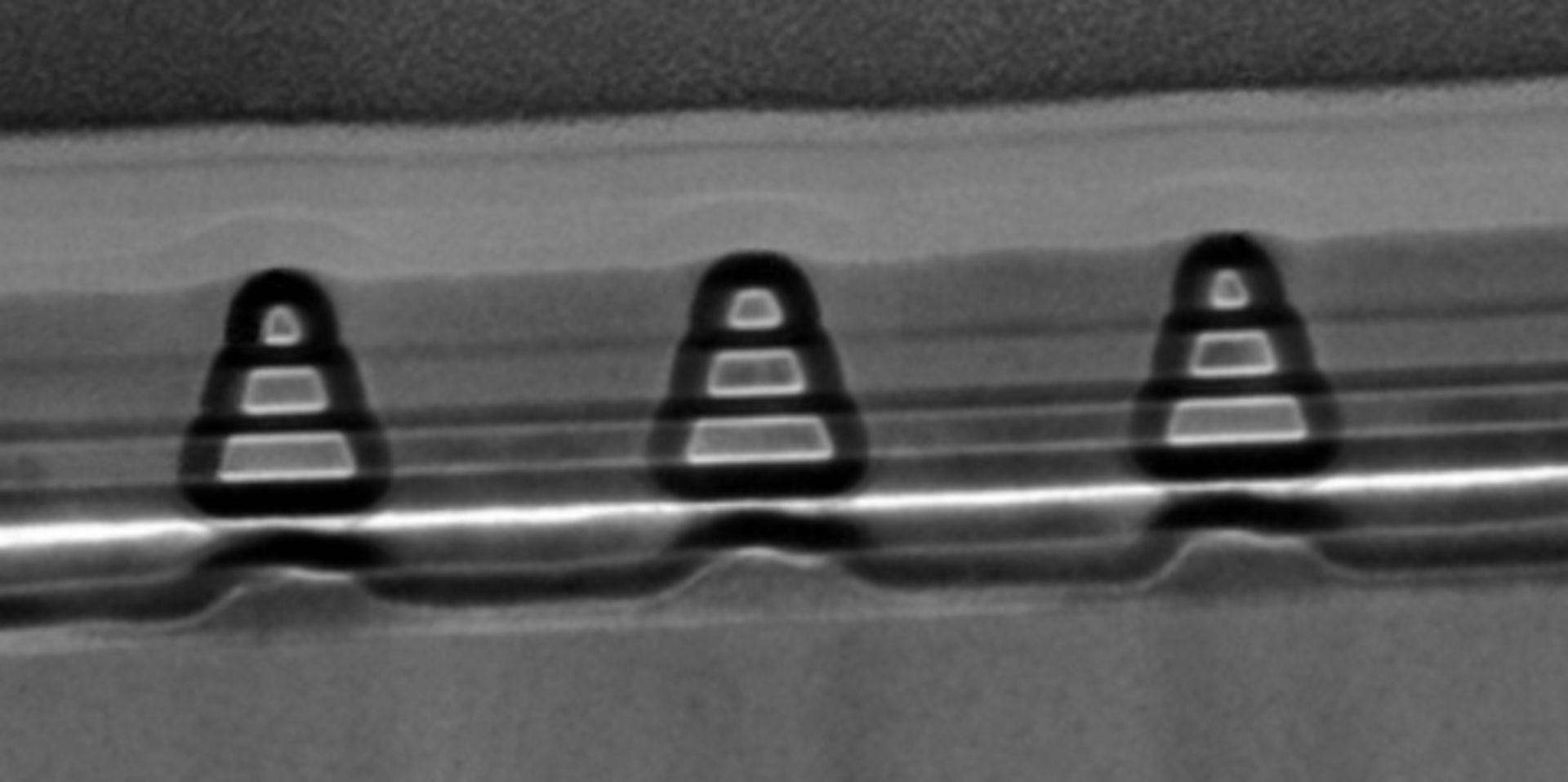

در ترانزیستورها برای جلوگیری از نشت ناخواستهی بار، ناحیهی کانال باید نازکتر شود تا مجالی برای نشت نباشد و دروازه، کانال را از اطراف احاطه کند. به همین دلیل، در ترانزیستورهای امروزی FinFET (ترانزیستور بالهی اثرمیدان)، ناحیهی کانال بهسمت خود کج شده است تا بالهی باریک سیلیکونی بین منبع و تخلیه شکل بگیرد و مسیری وسیعتر برای جریان فراهم سازد. البته، دروازه و دیالکتریک روی آن باله را پوشاندهاند و آن را برخلاف ترانزیستورهای قدیمیتر، از سه طرف احاطه کردهاند.

سیر تکامل FET (ترانزیستور اثرمیدان)

از زمان معرفی ترانزیستورها در سال ۱۹۵۹، ترانزیستور اثرمیدان عمدتا در سطح صافی از سیلیکون ساخته میشد؛ اما برای کنترل بهتر نشت جریان، شکل بالهای برجسته را بهخود گرفت و اکنون نیز در حال تبدیلشدن به حجم انبوهی از ورقها هستند.

بدون شک ساخت ترانزیستورهای FinFET موفقیت بزرگی بود. درحالیکه بیش از یک دهه از زمان معرفی FinFET سپری شده است، اولین ترانزیستوری که در سال ۲۰۱۱ اینتل، سامسونگ، TSMC و سایر شرکتها در قالب لیتوگرافی ۲۲ نانومتری از آن استفاده کردند، مبتنیبر این فناوری بود. در آخرین دورهی عمر قانون مور، بار کاری سیلیکونهای پیشرفته به دوش FinFET بود؛ اما درنهایت، دوران طلایی این ترانزیستورها نیز به پایان خواهد رسید.

با وجود پردازندههای سه نانومتری، دیگر FinFETها قادر به رفع نیازها نخواهند بود. فناوری FinFET درکنار مزایا، معایبی نیز دارد. بهعنوان مثال، این ترانزیستورها در طراحی محدودیتهایی دارند که در ترانزیستورهای مسطح قدیمی مطرح نبود. برای درک این مشکل، ابتدا باید بدانیم همواره میان سرعت ترانزیستور، مصرف برق، پیچیدگی ساخت و هزینهی آن نوعی تعادل وجود دارد و این تعادل ارتباط زیادی با عرض کانال دارد که در مراکز طراحی دستگاه، به آن Weff گفته میشود. اگر عرض کانال بیشتر باشد، ترانزیستور جریان بیشتری هدایت میکند و سریعتر خاموش و روشن میشود؛ اما بهطبع فرایند ساخت پیچیده و پرهزینهتری دارد.

در ترانزیستورهای مسطح، این تعادل بهسادگی با تنظیم هندسی کانال (شکل، اندازه و...) ایجاد میشود؛ اما بالهای که در FinFETها وجود دارد، از انعطافپذیری زیاد جلوگیری میکند. اتصالات فلزی که ترانزیستورها را در مدار بههم وصل میکنند، در لایههایی بالاتر از خود ترانزیستورها قرار دارند. به همین دلیل، بالههای ترانزیستور نمیتوانند ازنظر ارتفاع بدون برخورد به اتصالات فلزی در بالای ترانزیستور خیلی بلند باشند (مانند عرض در نمونههای مسطح). امروزه، طراحان تراشهها با ساخت ترانزیستورهای خاصی که چندین باله دارند، این مشکل را حل کردهاند.

یکی دیگر از کاستیهای FinFETها، این است که دروازهی آن بالهی سیلیکونی مستطیلیشکل را فقط از سه جهت احاطه میکند و قسمت پایینی به بدنه سیلیکونی متصل میشود. این اتصال موجب نشتی جریان هنگام خاموشبودن ترانزیستور میشود. محققان معتقدند برای کنترل کامل جریان در ناحیهی کانال، دروازه باید این قسمت را بهطور کامل احاطه کند.

محققان با دریافتن این نکته، در سال ۱۹۹۰ اولین وسیلهی سیلیکونی را معرفی کردند که در آن، دروازه بهطور کامل ناحیهی کانال را احاطه کرده بود. از آن زمان، گروهی از محققان روی دستگاههایی کار میکنند که بهاصطلاح به آنها «دروازهی همهطرفه» گفته میشود. محققان پس از بهحداقلرساندن نشت جریان، منطقهی کانال را تا سال ۲۰۰۳ به نانوسیم باریکی تبدیل کردند که از منبع و تخلیه عبور میکرد و از همهی جهات دروازه آن را احاطه کرده بود.

نانوسیمهای دروازهی همهطرفه بهدلیل کمعرضبودن کانال، نمیتوانند مبنای توسعهی ترانزیستورهای نسل جدید باشند. سیم باریک مجال کمی برای فرار الکترونها میسر میسازد؛ بنابراین، ترانزیستور وقتی باید خاموش باشد، خاموش میشود؛ اما درصورت روشنبودن ترانزیستور، بهدلیل نازکبودن سیم فضای کمی برای عبور جریان الکتریسته فراهم و کاهش جریان و ایجاد کندی در روند خاموش و روشن کردن ترانزیستور را باعث میشود.

با قراردادن نانوسیمها روی یکدیگر، میتوان Weff و جریان بیشتری تولید کرد. مهندسان سامسونگ در سال ۲۰۰۴ نسخهای از این پیکربندی را بهنام «کانال چندوجهی FET» رونمایی کردند؛ اما این کانال چندوجهی نیز محدودیتهایی داشت. بهعنوان مثال، همانند باله در FinFET، ارتفاع پشته نباید خیلی زیاد شود تا به لایهی اتصال برخورد کند یا با افزودن هر نانوسیمی بیش از حد مجاز ظرفیت دستگاه سرعت تعویض حالت روشن و خاموش ترانزیستور کندتر میشود. درنهایت، بهدلیل پیچیدگی ساخت نانوسیمهای باریک آنها اغلب در کنارههای ترانزیستور زبر و زمخت میشوند. این زبری میتواند از سرعت جریان بکاهد.

در سال ۲۰۰۶، یکی از مهندسان مؤسسهی تحقیقاتی CEA-Leti فرانسه ایدهی بهتری ارائه داد. وی بهجای استفاده از انبوهی از نانوسیمها برای عبور از منبع و تخلیه، از پشتهای از ورقهای نازک سیلیسیومی استفاده کرد. طبق این ایده در ترانزیستور کوچکتر با افزایش عرض کانال همراه با کنترل مداوم بیشتر، میتوان وسیلهای کممصرف با عملکرد بهتری تولید کرد. محققان IBM با هدایت یکی دیگر از مهندسان نشان دادند درواقع ترانزیستور ساختهشده از انبوهی از صفحات نانو، Weff بیشتری در مقایسه با ترانزیستورهای مبتنیبر فناوری FinFET بهدست میدهد که همان مقدار تراشه را اشغال میکنند. این ایده در سال ۲۰۱۷ به کار برده شد.

امتیاز دیگر طراحی نانوصفحات انعطافپذیری آنها است. این ویژگی در روند توسعهی ترانزیستورها پس از عرضهی تراشههای مذکور با استفاده از فناوری FinFET از دست رفته بود. در نانوصفحات میتوان برای تقویت جریان، صفحات را گسترده کرد یا برای کاهش مصرف برق، آنها را باریک کرد. محققان IBM صفحات را در پشتههای سهگانه با اندازههای مختلف از ۸ تا ۵۰ نانومتر قرار دادهاند.

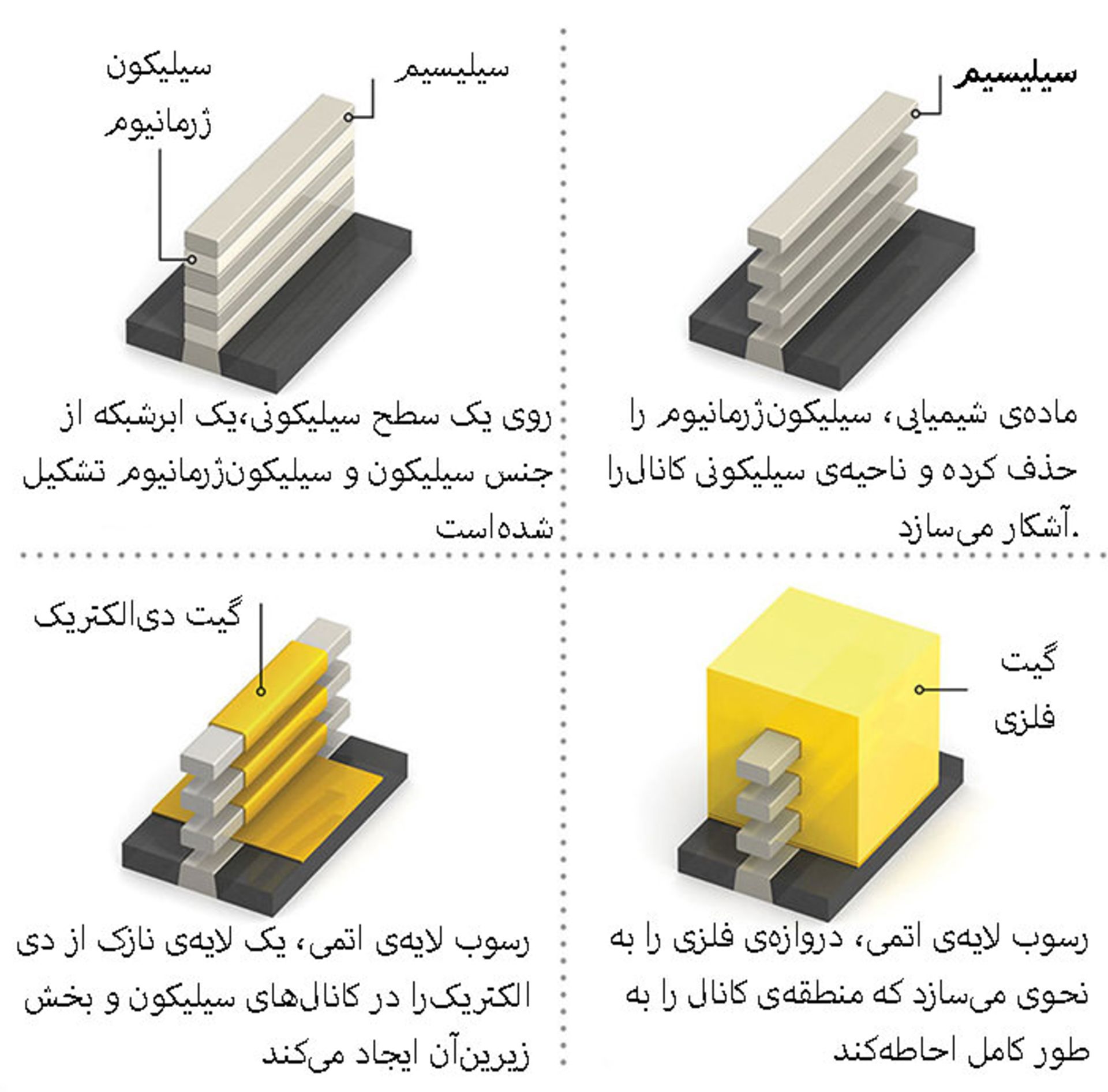

برای ساختن نانوصفحات لایهی قربانی (برای ساخت اجزای پیچیده مانند قطعات متحرک)، مواد شیمیایی با واکنشپذیری فراوان و فناوری دقیق و پیشرفتهی رسوب اتمی موردنیاز است. اغلب در فرایند ساخت نیمههادیها که سیلیکون ذوب و به بلور آن تبدیل میشود، تراشه باید صیقل داده و صاف شود و قطعات قسمتهای مختلف نیمههادی روی سطح تراشه بههم وصل شوند؛ به همین دلیل، ساخت نیمههادیها فرایندی زمانبر است. وظیفهی نانوصفحات پاکسازی مواد میان لایهها و پرکردن این فاصلهها با دیالکتریک و مواد دیگر است.

نکتهی اصلی در ساخت ترانزیستورها، نحوهی درستکردن ابرشبکه (Superlattice) (ساختار تناوبی از لایههای دو یا چند ماده) است که در ساخت ترانزیستورهای نانوصفحه از ابرشبکههایی با لایههای سیلیکون و ژرمانیم سیلیکون استفاده میشود. پژوهشگران ابرشبکههایی با ۱۹ لایه ساختهاند؛ ولی دو عامل شدت نیروهای درونی لایهها و افزایش ظرفیت ابرشبکه، استفاده از تعداد بیشتر لایهها را غیرمعقول جلوه میدهد.

بعد از اینکه ابرشبکهای با تعداد لایههای مناسب ساختیم، با استفاده از نوعی مادهی شیمیایی، لایههای ژرمانیم سیلیکون را حذف میکنیم؛ ولی لایههای سیلیکون همچنان باقی میمانند و نانوصفحات سیلیکون نیز مانند پلی میان منبع و تخلیه قرار میگیرند. استفاده از این لایهها ایدهی جدیدی نیست و ۲۰ سال پیش، مهندسان در شرکت مخابراتی فرنستلهکام و STMicroelectronic برای ساختن ترانزیستورهای آزمایشی «سیلیکون روی هیچچیز» از این لایهها استفاده کردند. این ترانزیستورها با نگهداشتن لایهای از هوا زیر محدودهی کانال ترانزیستور، سعی کردند معایب کانال کوتاه (عملکرد نامناسب و افزایش حرارت) را کاهش دهند.

نکتهی حیرتانگیز در ساخت ترانزیستورهای نانوصفحه که از انقراض قانون مور نیز جلوگیری کرده، استفاده از آلیاژ سیلیسیم در کانال ترانزیستور است.

پس از آنکه نانوصفحهی سیلیکونی بهعنوان پلی میان منبع و تخلیه قرار گرفت، باید شکافهای اطراف کانال را پر کنیم. برای این کار از فرایند رسوب لایهی اتمی استفاده میکنیم. این فرایند بیش از یک دههی قبل برای ساخت تراشههای نیمهرسانا معرفی شد و مطابق با آن، شکافها را ابتدا با دیالکتریک و سپس با مواد بهکاررفته در پشتهی دروازه پر میکنیم.

در این فرایند که «رسوب لایهی اتمی» نام دارد، نوعی مادهی گازی شیمیایی جذب سطح فوقانی تراشه میشود. حتی اگر تراشه زیر نانوصفحه باشد، بازهم این ماده جذب میشود و لایهای روی تراشه تشکیل میدهد، سپس، مادهی دوم برای واکنش نشاندادن با مادهی اول افزوده میشود و لایهای بسیار نازک از مواد موردنیاز مانند دیالکتریک دیاکسیدهافنیوم تشکیل میدهد. این فرایند بهاندازهای دقیق است که میتواند ضخامت لایهی رسوبشدهی نهایی را تا حد لایهای اتمی کنترل کند.

نکتهی حیرتانگیز در ساخت ترانزیستورهای نانوصفحه که از انقراض قانون مور نیز جلوگیری کرده، استفاده از آلیاژ سیلیسیم در کانال ترانزیستور است. تا حد زیادی آنچه در این بین مشکلاتی ایجاد میکند، گرما است. اگرچه با ساخت هر تراشه با لیتوگرافی کمتر مساحت کاهش مییابد، مقدار گرمایی که مدار مجتمع میتواند از بین ببرد (تراکم قدرت)، بیش از یک دهه است که در حدود ۱۰۰ وات بر سانتیمترمربع ثابت مانده است.

تراشهسازان برای ثابت نگهداشتن تراکم قدرت تراشهها تلاش بسیاری کردهاند. برای پایین نگهداشتن سطح دما، فرکانس پردازشی نباید از میزان چهار گیگاهرتز تجاوز کند؛ به همین دلیل، صنعت تولید تراشههای پردازشی به طراحیهای چندهستهای روی آورد. با استفاده از این طرح، چندین هستهی پردازشی با فرکانس پردازشی پایین عملکرد همان هستهی پرسرعت را ایفا میکرد و حتی گرمای کمتری نیز تولید میشد. برای افزایش دوباره و بیشتر فرکانس پردازشی تا جایی که استفاده از سیلیسیم به ما اجازه میدهد، ما به ترانزیستورهایی با بازده انرژی بیشتر نیازمندیم.

یکی از راهحلهای بالقوه برای ساخت ترانزیستوری با بازدهی انرژی بیشتر و تولید گرمای کمتر، استفاده از موادی مثل ژرمانیم یا نیمهرساناهای تشکیلشده از عناصر ستون سه و چهار جدول تناوبی مانند گالیمآرسنید در ناحیهی کانال است. بدینترتیب، الکترونها ۱۰ برابر سریعتر از حالتهای قبلی حرکت میکنند و سرعت خاموش و روشن شدن ترانزیستور نیز بیشتر میشود. بااینحال، مزیت اصلی تسریع حرکت الکترونها کاهش ولتاژ مصرفی دستگاه است که باعث بهینهشدن مصرف انرژی در ترانزیستور میشود.

در سال ۲۰۱۲، مهندسی با نام Ye با ساخت ترانزیستوری سه نانوصفحهای با استفاده از ایندیوم گالیومآرسنید، نیمهرسانای ستون سه و چهار جدول تناوبی و نیز الهام از پژوهشهای انجامشده روی ترانزیستورهای نانوسیم و ساختار ابرشبکه، به نتایج بسیار خوبی دست یافت. در این نوع ترانزیستور بهازای هر میکرومتر از عرض کانال، جریانی معادل ۹,۰۰۰ میکروآمپر عبور میکرد که این مقدار سهبرابر جریان عبوری در ترانزیستورهای مسطح ایندیوم گالیومآرسنید امروزی نوع MOSFET است.

با اینکه بازدهی انرژی ترانزیستور سه نانوصفحهای هنورهم بهمیزان مدنظر نرسیده است، این ترانزیستورها برای آیندهی مدارهای مجتمع پرسرعت با بازدهی انرژی بیشتر بسیار مهم هستند؛ چون اگر در آینده فرایند تولید ریزپردازندهها پیشرفت کند، ممکن است با قراردادن نانوصفحههای بیشتر بتوانیم میزان عملکرد را تا ۱۰ برابر افزایشدهیم. محققان آزمایشگاههای HRL در مالیبوی کالیفرنیا روی ترانزیستورهایی کار میکنند تا با قراردادن دهها نانوصفحه رویهم، دستگاه قدرتی نیتریدگالیم را بسازند.

البته، ایندیوم گالیومآرسنید تنها راه پیشرفت ترانزیستورها نیست؛ چراکه محققان نیمهرساناهای دیگری مثل ژرمانیم و آرسنید ایندیوم و آنتیمونیدگالیوم را کشف کردهاند که از حاملهای بار با تحرک بسیار زیاد بهره میبرند و میتوانند عامل پیشرفت ترانزیستورها باشند. بهعنوان مثال، محققان دانشگاه ملی سنگاپور بهتازگی با کنارهم قراردادن ترانزیستور نوع n ساختهشده از آرسنیدایندیوم و ترانزیستور نوع p ساختهشده از آنتیمونیدگالیوم، مدار مجتمع کامل CMOS (نیمهرسانای اکسیدفلز مکمل) ساختهاند.

باوجوداین، راهحل سادهتر برای استفاده از نیمهرساناهای دارای حاملهای بار، این است که از ژرمانیوم ناخالص استفاده کنیم؛ چراکه بهدلیل این ناخالصی، سرعت الکترونها و حفرههایی که حامل بار مثبت هستند، بسیار زیاد است. ناگفته نماند ازآنجاکه ژرمانیوم برای چنین صنعت حساس و دقیقی نامطمئن است و مشکلاتی درزمینهی فرایند تولید دارد، ممکن است در عمل، برخی مراحل را با ژرمانیم سیلیکون بهعنوان مادهی کانال انجام دهند.

درمجموع، بهنظر میرسد قراردادن نانوصفحات روی هم بهترین راه ممکن برای ساخت ترانزیستورهای آتی است. درحالحاضر، شرکتهای تراشهساز میتوانند روش مدنظر را بهزودی در دستورکار قرار دهند. همانطورکه همه پیشبینی میکنند، ترانزیستورهایی که با ادغام مواد نیمهرسانا با تحرک زیاد ساخته خواهند شد، آیندهی ترانزیستورها را رقم خواهند زد.