نقشه راه تولید اینتل تا سال ۲۰۲۹ منتشر شد

فناوریهای جدید و آتی در تولید تراشه (Process Node) از موضوعهای جذاب کنونی در دنیای سختافزار هستند. یکی از مباحث اصلی کنفرانس اخیر International Electron Devices Meeting سازمان IEEE نیز به همین موضوع اختصاص داشت. تقریبا همهی جلسههای رویداد مذکور به انواع فناوریهای هفت و پنج و سه نانومتری اختصاص داشت. دراینمیان، نقشهی راه اینتل در مسیر تراشهها و پردازندههای آتی از اخبار مهم کنفرانس بود که توجه بسیاری را بهخود جلب کرد.

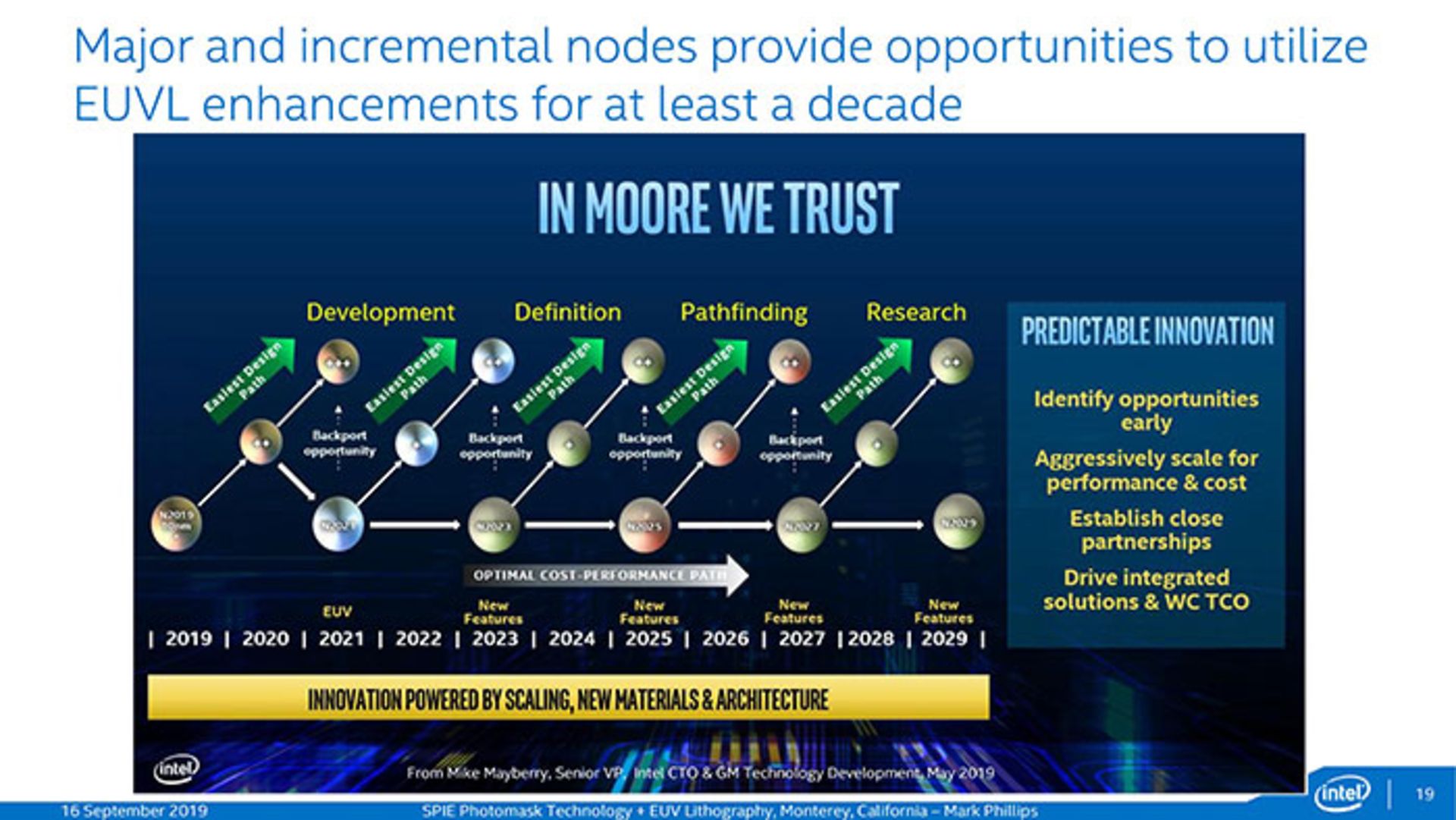

شرکت ASML، شریک تجاری اینتل، اسلایدی در کنفرانس بهنمایش گذاشت که با وجود تغییر جزئی، اطلاعات کاملی دربارهی نقشهی راه غول پردازنده نمایش میدهد. اسلایدها بهاندازهی چندین مقاله اطلاعات ارائه میکنند و با نگاهی به اسلاید ASML نیز میتوان اطلاعات مهمی دریافت.

تصویر پایین اسلاید اصلی است که شرکت اینتل ارائه داد؛ البته با نگاه اولیه به آن نمیتوان سال دستیابی به هر نود را پیشبینی کرد. بههرحال، مشخص است هریک از اِلِمانهای موجود در سطر پایینی تصویر، نشاندهندهی روش تولیدی (نود) هستند؛ درغیراینصورت علامتهای + و ++ در اسلاید بیمعنا می شدند.

ASML با تکیه بر اطلاعات اولیهی اینتل اسلایدی در رویداد IEDM ارائه کرد که در تصویر پایین مشاهده میکنید. البته آنها اعلام نکردند اسلاید کنونی، نسخهی تغییریافته از اطلاعات اصلی است. بههرحال باتوجهبه تصاویر، میتوان این نقشهی راه و مسیر را برای اینتل تفسیر کرد:

فناوری ۱/۴ نانومتر در سال ۲۰۲۹

اینتل انتظار دارد در مسیر تولید تراشهها، دورههای زمانی دوساله را پیش بگیرد. دورهها از روش تولید ۱۰ نانومتری در سال ۲۰۱۹ شروع میشوند و تراشههای ۷ نانومتری در سال ۲۰۲۱ ممکن خواهند شد. سپس در سالهای ۲۰۲۳، ۲۰۲۵، ۲۰۲۷ و ۲۰۲۹ شاهد نسخههای مهم جدید خواهیم بود. آخرین روش تولیدی که در اسلاید ASML دیده شد، ۱/۴ نانومتری نام دارد که اولینبار در اطلاعات مرتبط با این شرکت منتشر میشود. بههرحال، اگر روش تولید ۱/۴ نانومتری طبق تعریف بهمعنای ابعاد هر قطعهی واقعی باشد؛ یعنی قطعهای با ابعاد ۱۲ اتم سیلیکون خواهیم داشت.

در برخی از جلسههای کنفرانس امسال IEDM دربارهی ابعاد قطعات سختافزاری تراشههای آینده، ابعادی درحدود ۰/۳ میلیمتر با تعریف مواد «دوبعدی خودمونتاژ» مطرح میشد؛ درنتیجه شاید ادعای ۱/۴ نانومتری در اسلایدهای ASML دور از واقعیت نباشد. رسیدن به چنین ابعادی قطعا برای اینتل و شرکای تجاریاش بهمعنای مشکلات متعدد تولید خواهد بود.

+ و ++ و پیشانتقال

همانطورکه در اسلاید اینتل میبینیم، بین هر روش تولید مهم فازهای + و ++ وجود دارند که با هدف استخراج حداکثر توانایی از هر روش تولید رخ میدهند. تنها نمونهی استثناء در روش ۱۰ نانومتری دیده میشود که اکنون نمونههای +10nm را شاهد هستیم؛ درنتیجه در سالهای ۲۰۲۰ و ۲۰۲۱ شاهد ارائهی ++10nm و +++10nm خواهیم بود. اینتل میگوید توانایی ارائهی فازهای مذکور در دورههای یکساله را دارد؛ اما تیمهای مشترکی باید فعالیت کنند تا نودهای کاملا جدید همزمان با پیشرفت در فازهای + و ++ توسعه یابند.

نکتهی مهمی که در اسلایدها دیده میشود، اشاره به قابلیت پیشانتقال (Back Porting) است.قابلیت مذکور بهمعنای توانایی طراحی تراشه باتوجهبه روش تولیدی است که شاید بهدلیل تأخیرها بتوان آن را روی نسخههای قدیمی ++ روش تولیدی دیگر در همان دورهی زمانی تولید کرد. با اینکه اینتل میگوید طراحی تراشه را از فناوری روش تولید مجزا خواهد کرد، در برخی موارد باید برای شروع پیادهسازی الگوهای سیلیکونی به یک روش تولید پایبند ماند. در چنین موقعیتی، بهویژه در زمان ساخت ماسکهای تولیدی، فرایند تولید بهنوعی قفل میشود.

اینتل در اسلاید خود نشان میدهد روش کاری ممکن خواهد شد که هر طراحی هفت نانومتری نسل اول قابلیت پیشانتقال به ++10nm را داشته باشد. بههمینترتیب، هر نسل اول پنج نانومتری با ++7nm پیشانتقال میشود و روند ادامه پیدا میکند.

مراحل + و ++ باهدف بهرهبرداری از هر روش تولید بهصورت همزمان با طراحی جدید توسعه مییابند

برخی اعتقاد دارند شاید نتوان زمانبندی اسلایدهای اینتل را دقیق دانست. باتوجهبه اینکه روش تولید ۱۰ نانومتری اینتل زمان زیادی طول کشید، انتظار پیشرفتهای سالانه در ارائهی نمونههای + و ارائهی هر روش تولیدی هر دو سال یکبار شاید آنچنان منطقی بهنظر نرسد. درواقع، اسلایدهای منتشرشده فقط نشاندهندهی استراتژی خوشبینانه و تهاجمی اینتل هستند.

اینتل قبلا نیز قابلیت پیشانتقال را برای محصولات سختافزاری مطرح کرده بود. باتوجهبه تأخیرهای کنونی در فناوری تولید ۱۰ نانومتری اینتل، شایعهها ادعا میکردند شاید برخی از طراحیهای زیرمعماری پردازندهی مرکزی اینتل باتوجهبه روش ۱۰ نانومتری (+10nm یا ++10nm)، بهدلیل موفقیت روش ۱۴ نانومتری، براساس آن ساخته شوند.

توسعه و تحقیق

در فرایندهای تولید تراشه، عموما تیمهای متنوعی روی هر روش تولیدی کار میکنند. اسلاید کنونی نشان میدهد اینتل اکنون در مسیر بهینهسازی همزمان فرایند +++10nm و خانوادهی ۷ نانومتری قرار دارد. ایدهی اصلی این است که مراحل + بهمعنای بهرهبرداری از مزیتهای ابتدایی هر فرایند تولیدی باشند و با هر عدد جدید، نسل جدیدی از فرایند تولید معرفی شود. بههمینترتیب، میبینیم خانوادهی ۷ نانومتری اینتل براساس ++10nm طراحی میشوند و همین روال برای نسلهای بعدی ۵ و ۳ نانومتری هم ادامه مییابد. بدون شک برخی از بهینهسازیها که در هر بهروزرسانی + یا ++ ارائه میشوند، در طراحیهای آتی نیز درصورت نیاز بهکار گرفته خواهند شد.

در اسلاید جدید اینتل مشاهده میکنیم روش تولیدی سال ۲۰۲۳ اکنون در مراحل تعریف قرار دارد. همچنین، صحبتها و بحثهای کنفرانس IEDM در این دورهی زمانی دربارهی فناوری ۵ نانومتری است؛ ازاینرو، برخی از بهینهسازیهای فناورانه همچون مواد و روش تولید در فرایندهای اینتل هم وارد میشوند و وابسته به گروه طراحی همکار آنها هستند. شرکت Applied Materials از همکاران قدیمی غول پردازنده در این بخشهای محسوب میشود.

فناوری تولید ۵ نانومتری در سال ۲۰۲۳ مطرح شده است. ASML در همین دورهی زمانی فروش ماشینهای جدید لیتوگرافی فرابنفش خود موسوم به High NA را شروع میکند که قابلیت تعریف مسیر بهتر را در فرایندهای تولید بههمراه خواهد داشت. بههرحال، نمیتوان پیشبینی کرد دستگاه مذکور برای فرایند تولید ۵ یا ۳ نانومتری استفاده شود؛ اما بهصورت کلی میتوان تا حدودی اطلاعات منتشرشده را صحیح دانست.

اینتل پس از سال ۲۰۲۳ هنوز در وضعیت تحقیق و مسیریابی قرار خواهد داشت. چنین شرایطی مانند دورههای پیشین احتمالا بهمعنای تحقیق در مسیر یافتن مواد جدید و طراحی جدید برای ترانزیستورها خواهد بود. در کنفرانس کنونی IEDM، بحثهای متعددی دربارهی ترانزیستورهای gate-all-around میشود که بهنام nano-sheets یا nano-wires هم شهرت دارند؛ درنتیجه، بدون شک میتوان برخی از فناوریهای مذکور را با پایان عمر فناوری FinFET انتظار داشت.

TSMC اکنون از FinFET برای تولید ۵ نانومتری (برابر با ۷ نانومتری اینتل) استفاده میکند. بههرحال، جای تعجب نیست زمانی نانوشیتها و نانووایرها را در طراحی و تولید اینتل ببینیم. اسلایدهای بالا نکتهی جالب دیگری نیز دارند: اینتل هنوز به قانون مور اعتقاد دارد و شاید هزینهها و شکستهای متعدد در مسیر آن برایش بیمعنی باشد.