جزئیات تراشههای ۳ نانومتری TSMC منتشر شد: ۲۵۰ میلیون ترانزیستور در هر میلیمترمربع

شرکت صنایع نیمهرسانای تایوان موسومبه TSMC سالها است که در زمینهی تولید تراشه برای شرکتهایی نظیر اپل، کوالکام و هواوی فعالیت میکند؛ درواقع TSMC طراحی مدنظر را از این شرکتها دریافت و سپس محصول نهایی را بهمرحلهی تولید میرساند. فرقی ندارد که طراحی تراشهی موردبحث توسط چه شرکتی ارائه شده باشد؛ قانونی مهم درمورد همهی آنها صدق میکند: هرچه تعداد ترانزیستورهای داخل تراشه بیشتر باشد، تراشهی موردبحث قدرت پردازشی بیشتر و مصرف انرژی کمتری دارد.

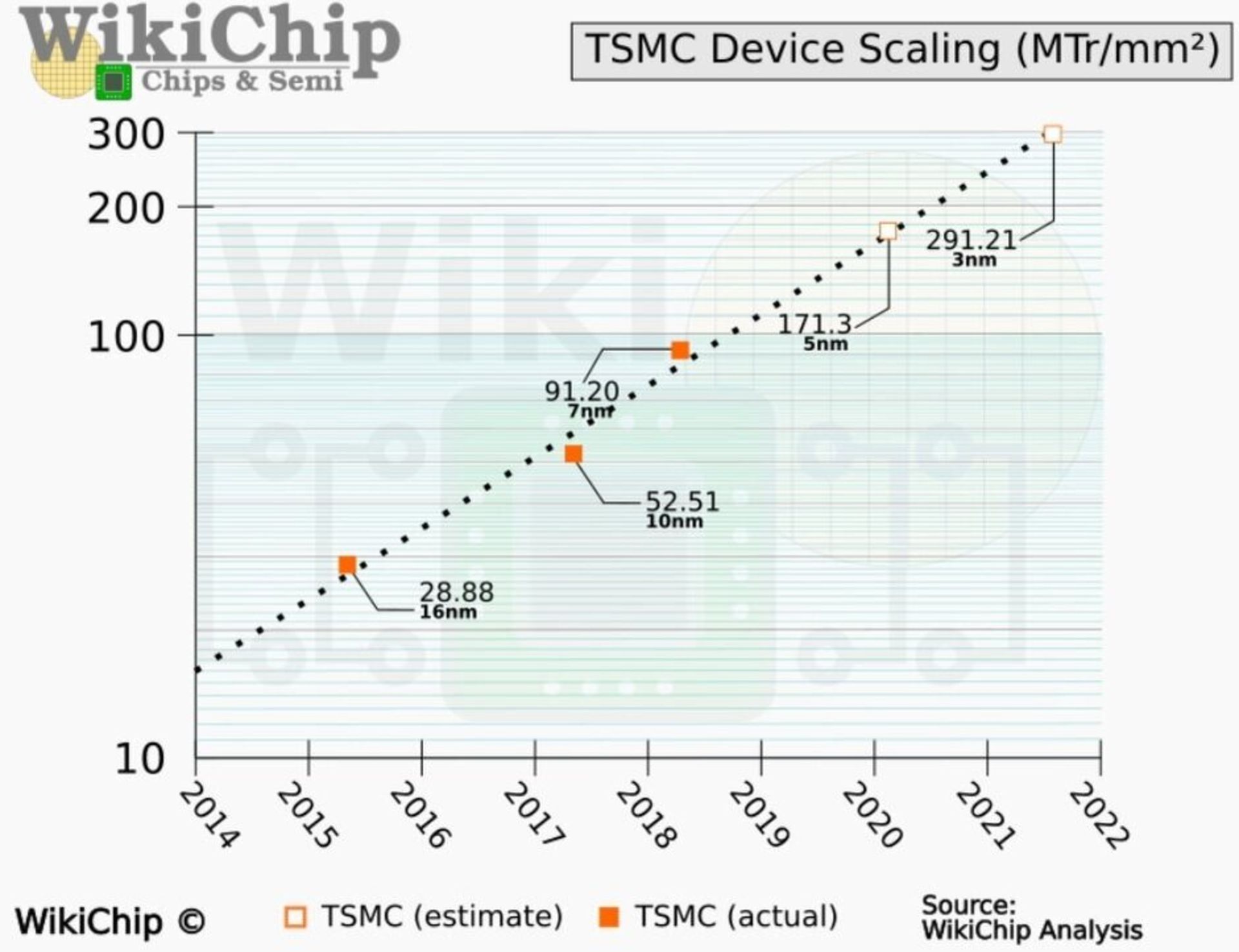

در رابطه با تراشهها معیاری با نام لیتوگرافی یا نود پردازشی (Process Node) مطرح میشود. لیتوگرافی به شمار ترانزیستورهایی مربوط است که شرکتهای تولیدی میتوانند آنها را در فضای خاصی از تراشهها، جای دهند؛ مساحت فضایی که ترانزیستورها در آن جای میگیرند معمولا در واحد میلیمترمربع (mm۲) بیان میشود. تراکم ترانزیستورهای موجود در تراشههایی نظیر A13 Bionic اپل و اسنپدراگون ۸۶۵ کوالکام و کرین ۹۹۰ 5G هواوی که امروزه با اتکا بر لیتوگرافی ۷ نانومتری ساخته میشوند، معادل تقریبا ۱۰۰ میلیون ترانزیستور در هر میلیمترمربع است.

لیتوگرافی پردازندهها قرار است تا چه زمانی روند کوچکتر شدن را ادامه دهد؟ تراشههای ۳ نانومتری بهصورت اولیه در سال آیندهی میلادی تولید خواهند شد. درضمن اخباری دیگر مدعی شدهاند که AMD قصد دارد بهزودی تراشههای ۵ نانومتری بسازد.

تراکم ترانزیستورها در لیتوگرافی ۳ نانومتری حدودا ۳/۶ برابر تراکم آنها در لیتوگرافی ۷ نانومتری است

تراکم یادشده به اپل امکان داده است ۸/۵ میلیارد ترانزیستور را در سیستم-روی-چیپ قدرتمند A13 جای دهد. همچنین هواوی توانسته است با استفاده از لیتوگرافی ۷ نانومتری EUV که متعلق به TSMC است در هر میلیمترمربع از تراشهی قدرتمند کرین ۹۹۰ 5G، بهطور میانگین ۹۰ میلیون ترانزیستور قرار دهد تا تعداد نهایی آنها در تراشه به ۱۰/۳ میلیارد عدد برسد. ناگفته نماند که این تراشه دارای اندازهی ۱۱۳/۳۱ میلیمترمربع است.

تراشههای مبتنیبر لیتوگرافی جدید ۵ نانومتری شامل ۱۷۱/۳ میلیون ترانزیستور در هر میلیمترمربع خواهند بود. براساس گفتههای سیسی وی، مدیر اجرایی ارشد TSMC، این شرکت تولید انبوه لیتوگرافی ۵ نانومتری را آغاز کرده است. ظاهرا TSMC انتظار دارد میزان تولید تراشههای ۵ نانومتری در نیمهی دوم سال جاری میلادی بهشکلی سریع افزایش پیدا کند. همچنین مدیر اجرایی ارشد TSMC گفته است که این شرکت انتظار دارد بتواند ۱۰ درصد از کل درآمد امسالش را از طریق تراشههای ۵ نانومتری بهدست بیاورد. سیسی وی همچنین میگوید لیتوگرافی ۵ نانومتری TSMC قرار است همچون لیتوگرافیهای پیشین نظیر ۷ نانومتری، ۱۶ نانومتری و ۲۸ نانومتری برای مدتزمانی طولانی در بازار حضور داشته باشد.

هرچه تعداد ترانزیستورها بیشتر باشد، تراشه قدرت پردازشی بیشتر و مصرف انرژی کمتر دارد

اگر اپل تراشهی A14 Bionic را با اتکا بر لیتوگرافی ۵ نانومتری تولید کند، خواهد توانست مجموع ۱۵ میلیارد ترانزیستور را در آن جای دهد. تراشهی A13 با ۸/۵ میلیارد ترانزیستور در زمینهی پردازشی هیولایی بیشاخودم است و عملکردی فوقالعاده از خود نشان میدهد. حال تصور کنید که A14 با ۱۵ میلیارد ترانزیستور چه قدرتی در زمینهی پردازش وظایف مختلف خواهد داشت. گفته میشود عملکرد تراشههای مبتنیبر لیتوگرافی ۵ نانومتری نسبتبه تراشههای ۷ نانومتری بهمیزان ۱۰ تا ۱۵ درصد افزایش پیدا خواهد کرد. بهعلاوه تراشههای ۵ نانومتری بین ۲۵ تا ۳۰ درصد کممصرفتر از ۷ نانومتریها خواهند بود.

قانون مور که نخستین بار توسط یکی از بنیانگذاران اینتل با نام گوردون مور در سال ۱۹۶۵ ارائه شد، قانونی جالب است که ادعا میکند تعداد ترانزیستورها در مدارهای مجتمع، هرسال دو برابر میشود. در دههی ۱۹۷۰ میلادی گوردون مور بازنگری مهمی در نظریهی خود مطرح کرد و و دورهی زمانی دو برابر شدن تراکم ترانزیستورهای تراشهها را به دو سال افزایش داد. بسیاری از مردم مدعی شدهاند که امروزه باید قانونی جدید با قانون مور جایگزین شود؛ این افراد میگویند نرخ افزایش تراکم ترانزیستورها بهشکل شگفتانگیزی در حال افزایش است و قانون مور، دیگر صدق نمیکند. از زمان مطرح شدن مور، گاهی اوقات شاهد نقض شدن این قانون بودهایم؛ اما مفهوم کلی قانون مور همچنان برقرار است.

هرچه زمان میگذرد با کوچکتر شدن لیتوگرافی پردازندهها، تراکم ترانزیستورهای بهکاررفته در آنها افزایش مییابد

امروزه سامسونگ و TSMC بهشدت در حال تلاش هستند تا بتوانند هرچه زودتر خطوط تولید کارخانههای خود را برای ساخت تراشههای مبتنیبر لیتوگرافی ۳ نانومتری راه بیندازند. هر دو شرکت مدتی پیش اعلام کردند که همهگیری ویروس کرونا و تعطیلی کارخانهها باعث شده است تاریخ عرضهی تراشههای ۳ نانومتری بهتعویق بیافتد. براساس ادعاهای مطرحشده از سوی رسانهی ویکیچیپ، تراشههایی که با لیتوگرافی ۳ نانومتری TSMC ساخته خواهند شد، با مصرف ۱۵ درصد انرژی کمتر، قدرت پردازشی ۵ درصد بهتری نسبتبه لیتوگرافی ۵ نانومتری از خود ارائه خواهند داد.

افزون بر این موارد گفته میشود که تراکم ترانزیستورها روی تراشههای ۳ نانومتری با رشدی ۱/۷ برابری به ۲۵۰ میلیون در هر میلیمترمربع خواهد رسید که در نگاه اول، شگفتانگیز است. ظاهرا TSMC قصد دارد تولید اولیه و غیرانبوه تراشههای ۳ نانومتری را در سال ۲۰۲۱ بهصورت رسمی آغاز کند. ظاهرا برخی از مشتریان TSMC از این شرکت درخواست کردهاند بدون بررسی دقیق و عیبیابی نمونههای اولیه، هرچه سریعتر تراشهی ۳ نانومتری را به دستشان برساند. حجم تولیدات تراشههای ۳ نانومتری در نیمهی دوم سال ۲۰۲۲ افزایش پیدا خواهد کرد و احتمالا TSMC نهایتا در سال ۲۰۲۳ فرایند تولید انبوه این تراشهها را شروع میکند. گزارشی جدید بهنقل از منابع غیررسمی مدعی شده است که بهدلیل بحران فعلی حاکم بر جهان بهدلیل همهگیری کووید ۱۹، سامسونگ نیز تصمیم گرفته است افزایش حجم تولید تراشههای ۳ نانومتری را از ۲۰۲۱ به ۲۰۲۲ بهتعویق بیاندازد.

TSMC احتمالا تولید اولیه و محدود تراشههای ۳ نانومتری را در سال ۲۰۲۱ آغاز میکند

سامسونگ و TSMC قصد دارند رویکردی متفاوت نسبتبه یکدیگر برای تولید تراشههای ۳ نانومتری در پیش بگیرند. TSMC از فناوری خود برای تولید تراشههای ۳ نانومتری با نام N3 یاد میکند. ظاهرا این شرکت در پی استفاده از ترانزیستورهای FinFET در فناوری N3 برای تولید تراشههای ۳ نانومتری است.

سیسی وی گفته است که فناوری N3 گام بزرگ مهمی برای TSMC بهشمار میآید و تراشههایی میسازد که تفاوتهایی عمده با تراشههای ۵ نانومتری خواهند داشت. ناگفته نماند ترانزیستورهای دارای FinFET از این فناوری برای کنترل بهتر جریان و ولتاژ برق در مدار بهره میگیرند. از طرفی گفته میشود سامسونگ دیگر قصد استفاده از ترانزیستورهای FinFET را ندارد و خودش را برای استفاده از فناوری MBCFET (مخفف Multi-Bridge-Channel FET) آماده میکند. تراشههای ۳ نانومتری سامسونگ در مقایسه با تراشههای ۷ نانومتری امروزی ۳۵ درصد عملکرد پردازشی بهتر و ۵۰ درصد مصرف انرژی کمتری خواهند داشت.

آیفون ۱۲ اپل احتمالا نخستین گوشی دنیا با تراشهی مبتنیبر لیتوگرافی ۵ نانومتری خواهد بود

MBCFET از نوعی فناوری ویژه با نام Gate All Around (یا GAA) استفاده میکند؛ کارکرد دقیق این فناوری بسیار پیچیده و در سطح تخصصی است، اما نتیجهای که بهدنبال میآورد کوچکتر و قدرتمندتر شدن ترانزیستورها برای استفاده در تراشهها است. یکی از مدیران اجرایی سامسونگ، ادعاهای جالبی مطرح کرده است؛ او میگوید سامسونگ در زمینهی استفاده از فناوری GAA بهمیزان حدودا ۱۲ ماه جلوتر از TSMC است. از طرفی طبق گفتهی این مقام اجرایی، اینتل در حدود ۲ تا ۳ سال پشت سر سامسونگ قرار دارد و فعلا نمیتواند به این شرکت برسد. سامسونگ میگوید فناوری GAA عصر تازهای از فعالیتهای این شرکت در حوزهی تولید تراشه را آغاز میکند.

فراموش نکنید پیش از رسیدن به تراشههای ۳ نانومتری، باید منتظر عرضهی دستگاههایی باشیم که از تراشههای مبتنیبر لیتوگرافی ۵ نانومتری استفاده میکنند. اگر همهچیز طبق برنامه پیش برود، گوشیهای خانوادهی آیفون ۱۲ اپل که احتمالا مجهز به فناوری 5G خواهند بود، از تراشهای ۵ نانومتری بهره خواهند گرفت؛ تراشهای که فعلا از نام غیررسمی A14 Bionic برای آن استفاده میشود. این یعنی احتمالا گوشی آیفون ۱۲ نخستین گوشی دنیا با تراشهی ۵ نانومتری خواهد بود. اگر ویروس کرونا برنامههای اپل را تغییر ندهد، موبایلهای خانوادهی آیفون ۱۲ اواخر شهریور امسال معرفی خواهند شد و در پاییز در دسترس قرار خواهند گرفت. درضمن گفته میشود گوشیهای خانوادهی میت ۴۰ هواوی قرار است نخستین دستگاههای اندرویدی مجهز به تراشهی ۵ نانومتری باشند.

شما کاربران زومیت چه دیدگاهی درمورد تراکم زیاد ترانزیستورها در تراشههای مبتنیبر لیتوگرافی ۳ نانومتری دارید؟