پتنت اپل، آینده احتمالی تراشههای این شرکت را به تصویر میکشد

اپل بهتازگی پتنتی ثبت کرده است که در آن شاهد سابسیستم ترکیبی برای حافظه هستیم که حداقل دو نوع حافظه را شامل میشود: یک نوع DRAM با پهنای باند زیاد و تراکم کم به همراه یک نوع DRAM با پهنای باند کم و تراکم زیاد. این پتنت احتمالا نخستین نگاه ما به ایدههایی است که این شرکت برای آیندهی سیستم-روی-چیپ (SoC) در سر میپروراند. براساس گزارش تامز هاردور، پتنت اپل ممکن است به طراحی مدلهای بعدی تراشهی M1 ارتباط داشته باشد؛ البته این نوع طراحی از لحاظ تئوری میتواند در چندین نوع تراشه استفاده شود.

پتنتها همواره به محصول واقعی تبدیل نمیشوند؛ اما براساس بازخورد یکی از وکلای حوزهی پتنت با نام کری کریران، به نظر میرسد اپل بهسختی تلاش و هزینه کرده است تا بتواند این تکنیک تولید تراشه را در تعداد زیادی از حوزههای قضایی سراسر دنیا ثبت کند. این موضوع نشان میدهد اپل بهطور جدی به عملی کردن این پتنت فکر میکند و احتمالا تراشهی بهنمایشدرآمده در پتنت قرار است بهصورت جهانی در محصولات اپل حضور پیدا کند.

معماری جدید سیستم، معماری جدید حافظه

مهاجرت اپل از پردازندههای مرکزی اینتل و پردازندههای گرافیکی مجزای ای ام دی (AMD) به تراشهی اختصاصی M1 اتفاق بسیار مهمی است. اپل با این کار معماری CPU رایانههای سری مک را از x86 به آرم و معماری GPU را از Radeon به معماری نشأتگرفته از PowerVR منتقل میکند و همین موضوع باعث ایجاد تحولی محسوس در مکها میشود.

پردازندهی مرکزی و پردازندهی گرافیکی مجزا دارای سابسیستم حافظهی (Memory Subsystem) مخصوص هستند؛ اما سیستم-روی-چیپ بهطور معمول به معماری یکپارچهی حافظه (Unified Memory Architecture - UMA) متکی است. معماری یکپارچهی حافظه در مقایسه با سابسیستمهای مستقل، چندین مزیت به ارمغان میآورد و یک نقطه ضعف بزرگ دارد: در سیستمهای مبتنی بر معماری یکپارچهی حافظه، واحدهای CPU و GPU باید ظرفیت حافظه و پهنای باند را به اشتراک بگذارند و همین موضوع میتواند در برخی سناریوهای مشخص، روی عملکرد کلی تراشه اثرگذار باشد.

حافظههای نوع HBM2 و HBM2E دارای پهنای باند بسیار زیاد هستند؛ اما استفاده از آنها در دستگاهها هزینهبر است و این نوع حافظهها انرژی زیادی مصرف میکنند و امکان ارتقا دادن آنها توسط کاربر وجود ندارد. متقابلا ساخت سابسیستم حافظه با ظرفیت زیاد و پهنای باند کافی برای پردازندهی گرافیکی ردهبالا با استفاده از حافظههای مرسوم یا GDDR، همیشه قابل انجام نیست و برخی محدودیتها متوجه شرکتها میشود.

اپل برای تزریق بیشترین توانایی به حافظه، پتنتی ثبت کرده است که طراحی منحصربهفردی را نشان میدهد. در این نوع طراحی شاهد سابسیستمِ ترکیبی برای حافظه هستیم که حافظههای شبه HBM و حافظههای شبه DDR را در کنار هم قرار میدهد.

طراحی ترکیبی اپل، حافظههای شبه HBM و حافظههای شبه DDR را در کنار هم قرار میدهد

پتنت اپل دارای این عنوان است: «سیستم حافظه با تراکم زیاد و پهنای باند کم در کنار حافظههای دارای تراکم کم و پهنای باند زیاد.» این پتنت چندین نوع سیستم-روی-چیپ را تشریح میکند که از DRAM با پهنای باند زیاد به همراه DRAM اصلی با ظرفیت زیاد استفاده میکنند.

پتنت اپل بهطور مشخص سیستم-روی-چیپ را پوشش میدهد نه رایانهی شخصی (PC)؛ بدین ترتیب به نظر میرسد تمامی حافظههای DRAM در پتنت اپل به لایهی زیرین یا به برد اصلی (مینبرد) لحیم شدهاند؛ دقیقا همچون تراشههای LPDDR4X که اپل در سیستم-روی-چیپ M1 استفاده میکند. معماری تشریحشده در پتنت نشان میدهد اپل در حداقل شماری از سابسیستمهای ترکیبی حافظه به دنبال استفاده از ماژول استاندارد حافظه نیست.

اپل در بخش توضیحات پتنت میگوید در برخی از تصاویرِ ثبتشده، دو نوع DRAM سیستم حافظه را تشکیل میدهند که یکی از آنها ممکن است برای پهنای باند و دیگری برای حافظه بهینهسازی شوند. هدف اصلی از افزایش پهنای باند و ظرفیت حافظه، قابل درک است و شماری از نسخههای سابسیستم ترکیبی حافظه ممکن است روی بهبود مصرف انرژی تمرکز کنند؛ شرکت کوپرتینویی ادعا میکند در این شرایط «راهکاری بسیار کممصرف برای تولید حافظه ارائه میشود که هم قدرت پردازشی زیادی دارد و هم از پهنای باند زیاد استفاده میکند.»

اپل در دستهی شرکتهای تولیدکنندهی PC قرار میگیرد و بهطور کلی تمرکز اصلی خود را معطوف نوتبوک میکند؛ به همین دلیل وقتی موضوع کاهش مصرف انرژی را در معماری جدید اپل برای سابسیستم حافظه مشاهده کردیم، اصلا متعجب نشدیم. در کنار کاهش مصرف انرژی، بدیهی است که اپل تمایل دارد به پهنای باند و ظرفیت بیشتر برای حافظه دست پیدا کند.

اپل در پتنت جدید، با چند فناوری بین DRAM کش و DRAM اصلی ارتباط برقرار میکند

این پتنت اپل غالبا چندین نوع سابسیستم ترکیبی حافظه را به نمایش میگذارد که در آنها شاهد برقراری ارتباط بین DRAM کش و DRAM اصلی از طریق چندین فناوری هستیم. برای مثال در یکی از تصاویر پتنت، شاهد استفاده از TSV (Through-Silicon Via) هستیم که از درون بستهای از تراشههای حافظهی DRAM اصلی عبور میکند؛ این تکنیک باعث میشود بتوان ظرفیت تقریبا در خور توجهی از حافظهی DRAM را بدون اشغال کردن فضای زیاد، استفاده کرد. با وجود تمامی جزئیاتی که اپل منتشر کرده است، هنوز بهطور دقیق نمیدانیم که سیستمهای عامل و نرمافزارها قرار است چگونه از مزیتهای سابسیستم ترکیبی حافظه استفاده کنند.

یک فناوری مهم

اپل همچون دیگر شرکتهای بزرگ حوزهی فناوری در طول هر سال صدها پتنت در حوزههای مختلف ثبت میکند. شماری از این پتنتها در نهایت به محصول واقعی تبدیل میشوند؛ اما این اتفاق برای سایر آنها رخ نمیدهد. پتنت US10573368B2 اپل ظاهرا در سال ۲۰۱۶ ثبت شده است و سپس شرکت کوپرتینویی تلاش کرده سندهای مرتبط متعددی در بسیاری از حوزههای قضایی سراسر دنیا به ثبت برساند. همانطور که بالاتر اشاره کردیم، این موضوع میتواند نشان دهد معماری این پتنت قرار است بهصورت جهانی در بسیاری از محصولات این شرکت مورد استفاده قرار بگیرد.

کری کریران، وکیل شرکت Banner & Witcoff، میگوید پتنت اپل در بسیاری از حوزههای قضایی ثبت شده است که شامل سازمان ثبت اختراعات اروپا (EP)، ایالات متحدهی آمریکا، چین و ژاپن میشود. براساس گفتههای کریران، انجام این کار هزینههای زیادی در پی دارد و منطقیترین توضیح این است که محصول بهنمایشدرآمده در پتنت اهمیت زیادی دارد.

نکتهی جالب دیگر به نام یکی از مخترعان پتنت مربوط میشود: سوکالپا بیسوا. تامز هاردور مینویسد سوکالپا بیسوا از شرکت PA Semi به اپل ملحق شده است و به همین دلیل قطعا اطلاعات بسیار زیادی دربارهی طراحی پردازندهی مرکزی دارد.

ایدهی اصلی در انحصار اپل نیست

پتنت اپل برای سابسیستم ترکیبی حافظه تا حد زیادی تحسینبرانگیز به نظر میرسد؛ اما فکر نمیکنیم این نوع فناوری ترکیبی در انحصار اپل باشد.

پردازندههای مدرن کلاس سرور اینتل با نام Xeon Scalable میتوانند همزمان با ماژولهای SDRAM مرسوم DDR4 بههمراه ماژولهای (Optane Memory (3D XPoint کار کنند؛ یعنی این پردازندههای اینتل اساسا مبتنی بر سابسیستم ترکیبی برای حافظه هستند. پردازندههای نسل بعد سری Xeon Scalable اینتل که با کدنام سفایر رپیدز (Sapphire Rapids) شناخته میشوند از حافظهی HBM نیز پشتیبانی میکنند؛ به همین دلیل انتظار داریم سابسیستم حافظهی پردازندههای سری سفایر رپیدز شبیه به آن چیزی باشد که اپل در پتنتش به نمایش گذاشته است.

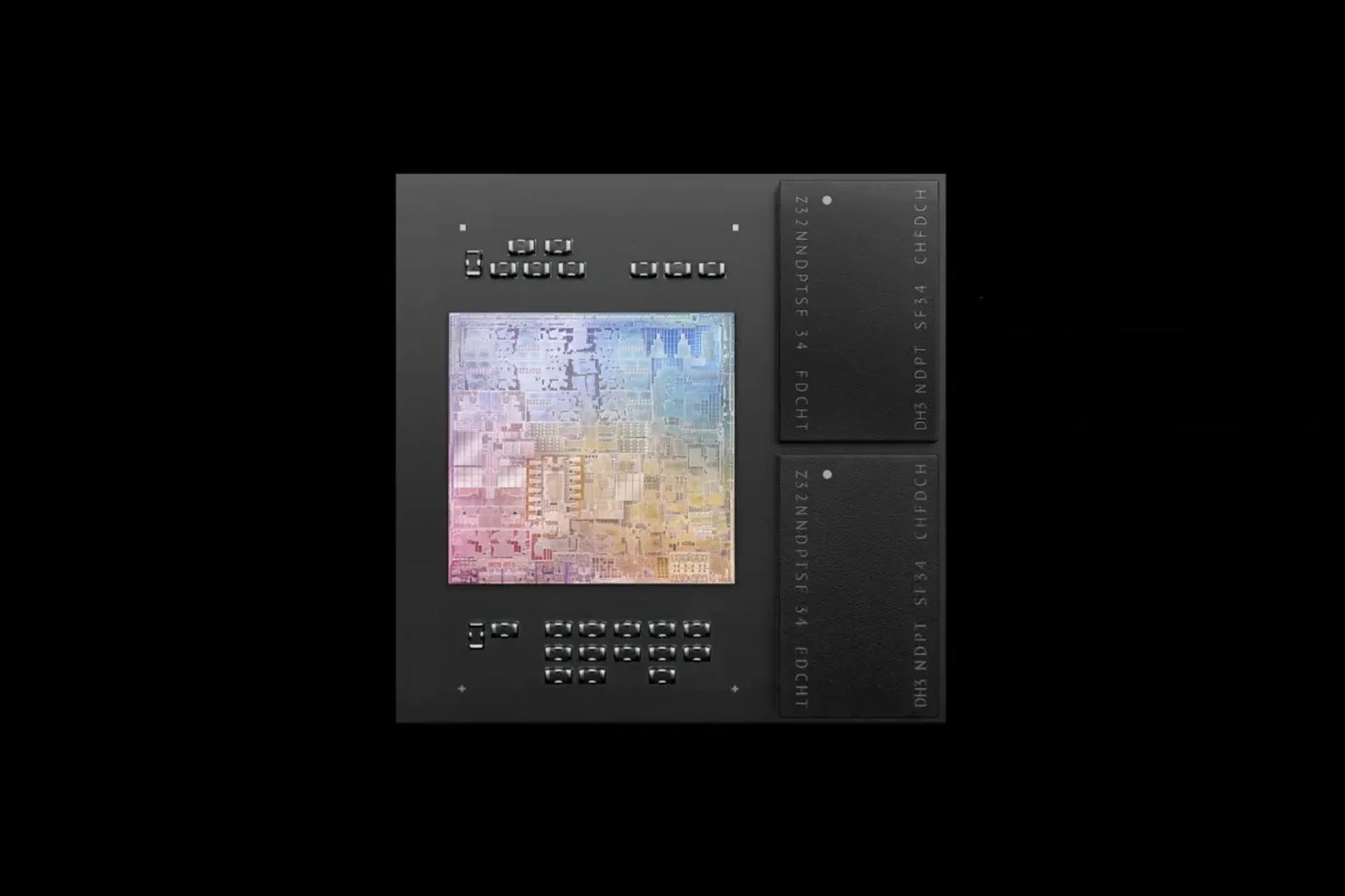

تصویر اصلی مقاله، پردازندهی M1 را نشان میدهد.

نظرات