TSMC لیتوگرافی 2 نانومتری N2 را با وعده ۵۶ درصد عملکرد بهتر از N5 معرفی کرد

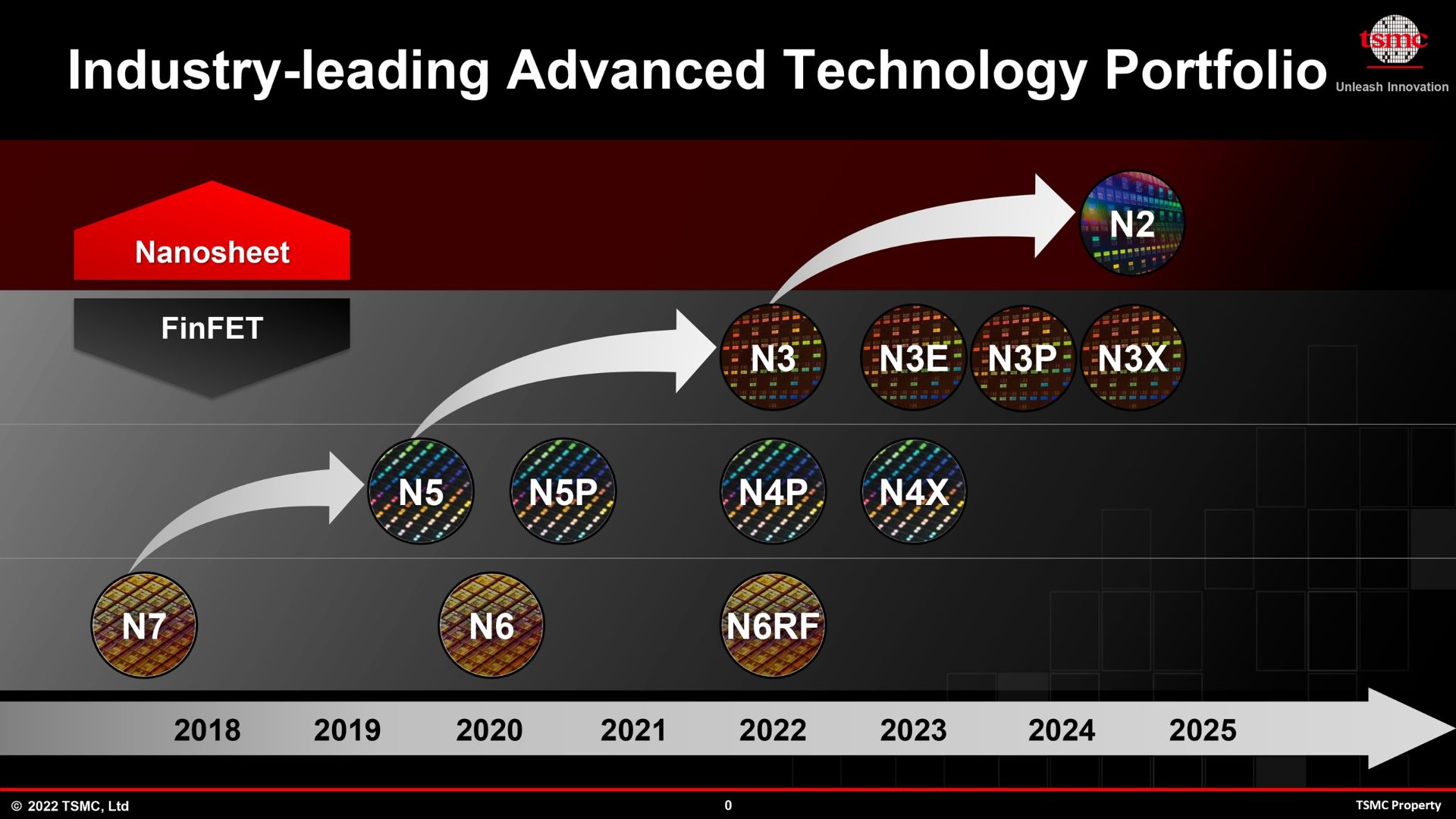

TSMC روز ۱۵ ژوئن ۲۰۲۲ در جریان رویدادی با عنوان Technology Symposium، بهطور رسمی از لیتوگرافی ۲ نانومتری N2 رونمایی کرد. این شرکت بهطور معمول در رویداد سالانهی خود جزئیاتی دربارهی برنامههای گسترش خطوط تولید را به اشتراک میگذارد و این بار نیز به گزارش AnandTech، این تولیدکننده، نسل جدیدی از نودهای پردازشی دو نانومتری (N2) هستند معرفی کرده است.

با پیچیدهتر شدن لیتوگرافی پردازندهها، تولیدکنندگان تراشه برای تولید محصولاتی با بازده و عملکرد بالاتر و مصرف کمتر با هم رقابت میکنند. در همین راستا، TSMC نیز قصد دارد تقریباً دو سال و نیم پس از معرفی N3، نسل جدیدی از لیتوگرافی را به بازار عرضه کند. در این فناوری N2 برای اولین بار ترانزیستورهای کاملاً جدید GAAFET به کار میروند که از صفحاتی با ضخامت نانو ساخته شدهاند. استفاده از این ترانزیستورها این امکان را فراهم میکند تا تولیدکنندگان بدون کاهش عملکرد یا تراکم، مصرف برق تراشهها را بهطور قابل توجهی کاهش دهند. بنابراین انتظار میرود تفاوت بین ویفرهای سه نانومتری و ویفرهای دو نانومتری TSMC بسیار زیاد باشد.

فناوری N2، پلتفرمی کاملاً جدید از TSMC است که علاوه بر بهرهمندی گسترده از لیتوگرافی EUV و GAAFETها (یا ترانزیستورهای نانوصفحهای) و به فناوری خاصی برای تحویل توان نیز مجهز است که با کاهش تراکم مسیریابی در انتهای خط، به بهینهسازی مصرف برق کمک میکند.

ساختار جدید قرارگیری سراسری ترانزیستورها روی گیت و تعبیه کردن گیتها در هر چهار طرف کانالها، کاهش چشمگیر نشتی جریان و همچنین توانایی تنظیم عرض کانال برای افزایش کارایی یا کاهش مصرف برق را نوید میدهند. فناوری تحویل توان نیز در این ساختار عموماً به گونهای طراحی شده است که امکان انتقال بهینهی توان به ترانزیستورها را فراهم کرده و افزایش مقاومتها را از بین میبرد. بهطور کلی، فرایند N2 عملکرد ترانزیستور را افزایش داده و مصرف انرژی را کاهش میدهد؛ این قابلیتها میتوانند بسیار امیدوارکننده باشند.

N2 درمقابل N3E | N3E درمقابل N5 | N3 درمقابل N5 | N5 درمقابل N7 | |

|---|---|---|---|---|

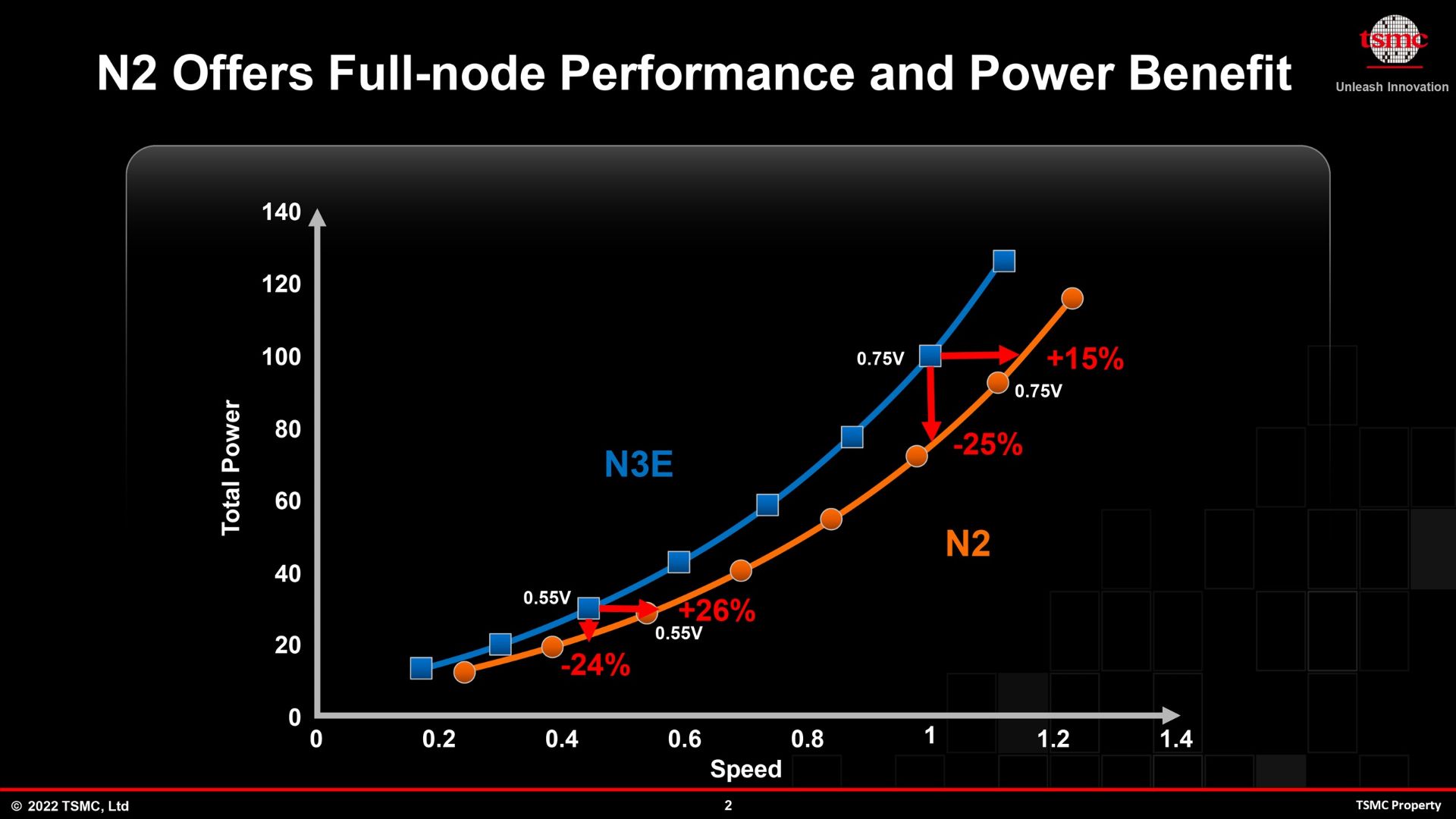

بهبود عملکرد در توان یکسان | ۱۰ تا ۱۵ درصد | ۱۸ درصد | ۱۰ تا ۱۵ درصد | ۱۵ درصد |

توان مصرفی در فرکانس یکسان | بین ۲۵ تا ۳۰ درصد کمتر | ۳۴ درصد کمتر | بین ۲۵ تا ۳۰ درصد کمتر | ۳۰ درصد کمتر |

تراکم ترانزیستور | بیش از ۱٫۱ برابر | حدود ۱٫۳ برابر | - | - |

تاریخ آغاز تولید انبوه | نیمهی دوم ۲۰۲۵ | سهماهه دوم و سوم ۲۰۲۳ | نیمهی دوم ۲۰۲۲ | سهماهه دوم ۲۰۲۲ |

طبق ادعای TSMC، تولیدکنندگان تراشه با استفاده از لیتوگرافی جدید دو نانومتری N2 و افزایش بیش از ۱٫۱ برابری تراکم نسبت به گرهی N3E این شرکت، میتوانند عملکرد تراشههای خود را بین ۱۰ تا ۱۵ درصد افزایش داده و مصرف برق را نیز در فرکانس و پیچیدگی یکسان بین ۲۵ تا ۳۰ درصد کاهش دهند. با انجام محاسبات ریاضی و با استناد به اعداد و ارقامی که TSMC عنوان کرده است، میتوان حساب کرد که گرهی ۲ نانومتری N2 نسبت به گرهی N5، حدود ۶۵ درصد عملکرد بهتری ارائه میکند.

بهبود عملکرد و کاهش مصرف گرهی N2 در مقایسه با N3E، با آنچه که TSMC ادعا میکند مطابقت دارد. بااینحال چگالی تراشه (که باید منعکسکنندهی افزایش چگالی ترانزیستور باشد) تنها کمی بیش از ۱۰ درصد است، که آنچنان چشمگیر به نظر نمیرسد، چراکه تراکم ترانزیستور در گرهی N3E تنها کمی کمتر از گرهی N3 است. در نظر داشته باشید که این روزها به جای بهبود SRAM و مدارهای آنالوگ، تراکم ترانزیستور تراشهها بهبود پیدا میکنند، اما بهبود ۱۰ درصدی تراکم تراشه در مدت سه سال برای پردازندههای گرافیکی و سایر تراشهها دستاوردی قابل توجه محسوب نمیشود.

به نظر میرسد TSMC قصد دارد در اقدامی نوآورانه، همزمان با توسعهی گرهی N2، گرهی N3S بهینهسازیشدهای برای چگالی را نیز توسعه داده و دو فناوری با تراکم ترانزیستورهای بسیار مشابهی را ارائه دهد.

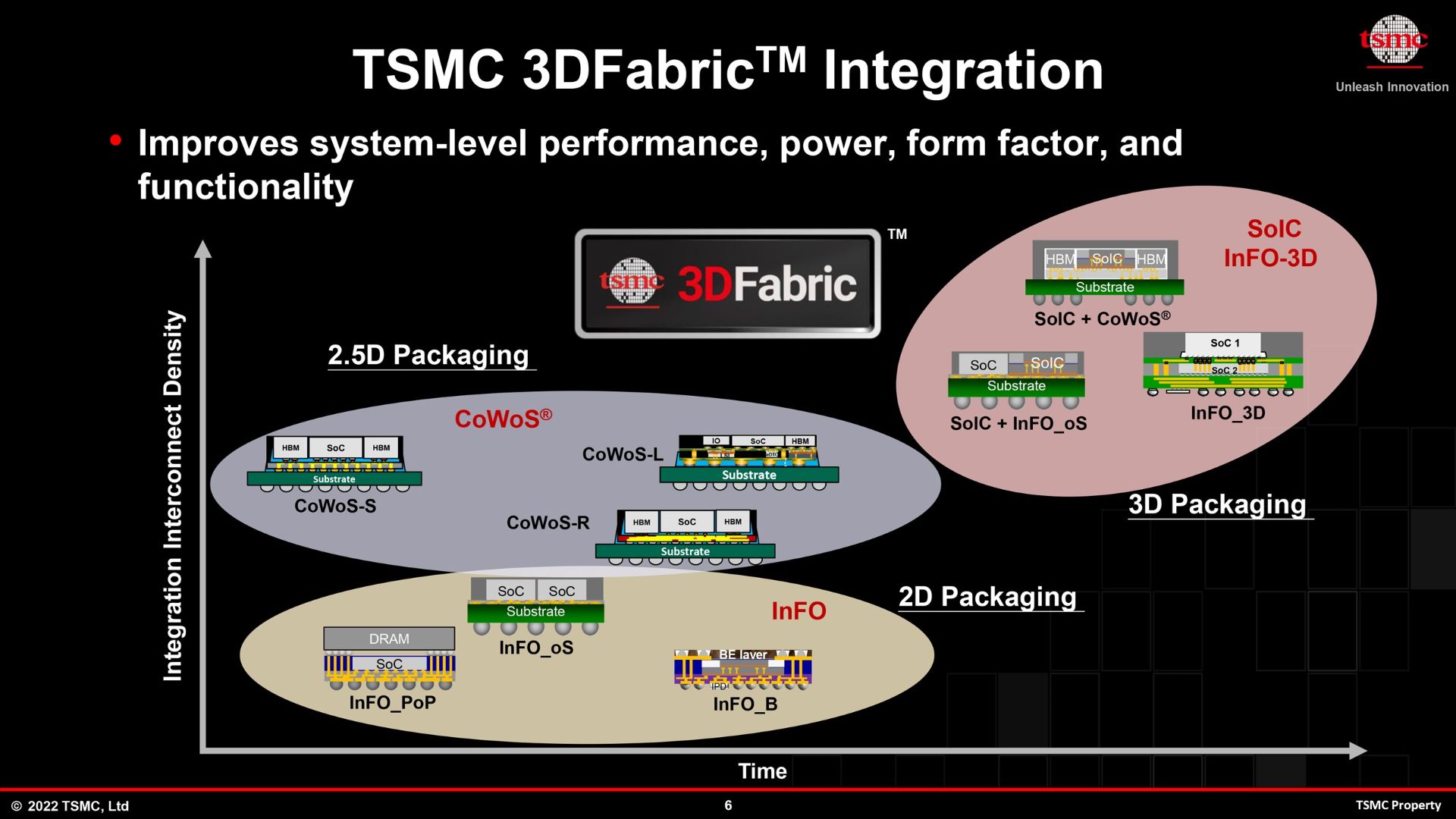

طبق روال TSMC، این شرکت گرهی N2 خود را با بهرهمندی از قابلیتهای مختلفی ارائه میکند که به طراحان تراشه اجازه دهد هر تراشهای از پردازندههای لپتاپی کممصرف گرفته تا پردازندههای گرافیکی بالارده را به بهینهترین شکل ممکن طراحی کنند. علاوه بر این پلتفرم جدید TSMC، از قابلیت جدیدی به نام یکپارچهسازی تراشه نیز پشتیبانی میکند که احتمالاً به یکپارچهسازی تراشههای N2 را در بستههای چند تراشهای با گرههای مختلف اشاره دارد. ازآنجاکه سرعت تغییر مقیاس تراکم ترانزیستورها، در حال کاهش بوده و هزینهی توسعهی فناوریهای فرایند جدید نیز با گذشت زمان افزایش پیدا میکند؛ در چند سال آینده شاهد استفادهی بیشتر توسعهدهندگان از بستههای چند تراشهای برای بهینهسازی طراحی و هزینههای خود خواهیم بود.

انتظار میرود فرایند تولید اولیه و آزمایشی تراشهها با استفاده از فرایند ساخت N2، در نیمه ی دوم ۲۰۲۴ آغاز شود و در نیمه دوم ۲۰۲۵ نیز این فرایند به تولید انبوه برسد. البته با توجه به چرخههای تولید قطعات نیمههادی، بهتر است تا اواخر سال ۲۰۵ یا اوایل ۲۰۲۶ منتظر تراشههای تولید شده با این فرایند نباشیم.